-

1.1目录

-

1.21 常用电子仪器

-

1.2.11.1 DF4325型示波器

-

1.2.1.11.1.1 面板上控制键的名称及功能说明

-

1.2.1.21.1.2 使用说明

-

1.2.1.2.11)测定前的检查

-

1.2.1.2.22)操作方法

-

1.2.1.2.33)测量

-

1.2.21.2 SG1641A型函数信号发生器

-

1.2.2.11.2.1 主要性能

-

1.2.2.21.2.2 面板上按键、旋钮的名称及功能说明

-

1.2.2.31.2.3 使用说明

-

1.2.31.3 DT98型数字万用表

-

1.2.3.11.3.1 主要性能

-

1.2.3.21.3.2 安全事项

-

1.2.3.31.3.3 使用说明

-

1.2.3.3.11)交、直流电压(ACV、DCV)的测量

-

1.2.3.3.22)交、直流电流(ACA、DCA)的测量

-

1.2.3.3.33)电阻的测量

-

1.2.41.4 数字电路实验箱

-

1.2.4.11.4.1 实验箱的结构

-

1.2.4.21.4.2 使用说明

-

1.2.4.31.4.3 实验注意事项

-

1.32 数字逻辑电路实验

-

1.3.12.1 基本实验

-

1.3.1.12.1.1 门电路逻辑功能测试

-

1.3.1.1.11) 实验目的

-

1.3.1.1.22)实验原理和参考电路

-

1.3.1.1.33)实验内容和步骤

-

1.3.1.1.44)实验器材

-

1.3.1.1.55)预习要求

-

1.3.1.1.66)实验报告要求

-

1.3.1.1.77)思考题

-

1.3.1.22.1.2 触发器逻辑及应用

-

1.3.1.2.11)实验目的

-

1.3.1.2.22)实验原理和参考电路

-

1.3.1.2.33)实验内容及步骤

-

1.3.1.2.44)实验器材

-

1.3.1.2.55)预习要求

-

1.3.1.2.66)实验报告要求

-

1.3.1.2.77)思考题

-

1.3.22.2 设计型实验

-

1.3.2.12.2.1 一位大小比较器、全加器的设计

-

1.3.2.1.11)实验目的

-

1.3.2.1.22)实验原理

-

1.3.2.1.33)实验内容和步骤

-

1.3.2.1.44)实验器材

-

1.3.2.1.55)预习要求

-

1.3.2.1.66)实验报告要求

-

1.3.2.1.77)思考题

-

1.3.2.22.2.2 数据选择器、译码器的应用

-

1.3.2.2.11)实验目的

-

1.3.2.2.22)实验原理

-

1.3.2.2.33)实验内容和步骤

-

1.3.2.2.44)实验器材

-

1.3.2.2.55)预习要求

-

1.3.2.2.66)实验报告要求

-

1.3.2.2.77)思考题

-

1.3.2.32.2.3 集成计数器的设计

-

1.3.2.3.11)实验目的

-

1.3.2.3.22)实验原理和参考电路

-

1.3.2.3.33)实验内容和步骤

-

1.3.2.3.44)实验器材

-

1.3.2.3.55)预习要求

-

1.3.2.3.66)实验报告要求

-

1.3.2.3.77)思考题

-

1.3.32.3 综合应用型实验

-

1.3.3.12.3.1 计数、译码和显示电路

-

1.3.3.1.11)实验目的

-

1.3.3.1.22)实验原理和参考框图

-

1.3.3.1.33)实验内容及步骤

-

1.3.3.1.44)实验器材

-

1.3.3.1.55)预习要求

-

1.3.3.1.66)实验报告要求

-

1.3.3.1.77)思考题

-

1.3.3.22.3.2 移位寄存器及其应用

-

1.3.3.2.11)实验目的

-

1.3.3.2.22)实验原理和参考电路

-

1.3.3.2.33)实验内容及步骤

-

1.3.3.2.44)实验器材

-

1.3.3.2.55)预习要求

-

1.3.3.2.66)实验报告要求

-

1.3.3.2.77)思考题

-

1.3.3.32.3.3 555集成定时器及其应用

-

1.3.3.3.11)实验目的

-

1.3.3.3.22)实验原理和参考电路

-

1.3.3.3.33)实验内容及步骤

-

1.3.3.3.44)实验器材

-

1.3.3.3.55)预习要求

-

1.3.3.3.66)实验报告要求

-

1.3.3.3.77)思考题

-

1.3.3.4<span class="superscript">*</span>2.3.4 数模(D/A)和模数...

-

1.3.3.4.11)实验目的

-

1.3.3.4.22)实验原理和参考电路

-

1.3.3.4.33)实验内容及步骤

-

1.3.3.4.44)实验器材

-

1.3.3.4.55)预习要求

-

1.3.3.4.66)实验报告要求

-

1.43 EWB——电子电路设计仿真

-

1.4.13.1 概述

-

1.4.23.2 EWB的基本界面

-

1.4.2.13.2.1 EWB的主窗口

-

1.4.2.23.2.2 EWB的工具栏

-

1.4.2.33.2.3 EWB的元器件库

-

1.4.2.3.11)自定器件库(Favorites)

-

1.4.2.3.22)信号源库(Source)

-

1.4.2.3.33)基本器件库(Basic)

-

1.4.2.3.44)二极管库(Diode)

-

1.4.2.3.55)晶体管库(Transistors)

-

1.4.2.3.66)模拟集成电路库(Analog ICs)

-

1.4.2.3.77)混合集成电路库(Mixed ICs)

-

1.4.2.3.88)数字集成电路库(Digital ICs)

-

1.4.2.3.99)逻辑门电路库(Logic Gates)

-

1.4.2.3.1010)数字器件库(Digital)

-

1.4.2.3.1111)指示器件库(Indicators)

-

1.4.2.3.1212)控制器件库(Controls)

-

1.4.2.3.1313)其他器件库(Miscellaneous)

-

1.4.2.3.1414)仪器库

-

1.4.33.3 EWB的基本操作方法

-

1.4.3.13.3.1 EWB电路的创建与运行

-

1.4.3.23.3.2 EWB的基本操作方法

-

1.4.3.2.11)元器件的操作

-

1.4.3.2.22)导线的操作

-

1.4.3.2.33)仪器的操作

-

1.4.3.33.3.3 EWB软件自配仪表的使用

-

1.4.3.3.11)数字多用表的使用

-

1.4.3.3.22)示波器的使用

-

1.4.3.3.33)函数信号发生器的使用

-

1.4.3.3.44)字信号发生器的使用

-

1.4.3.3.55)逻辑分析仪的使用

-

1.4.3.3.66)逻辑转换仪的使用

-

1.4.3.43.3.4 帮助功能的应用

-

1.54 数字逻辑电路(EWB仿真)实验

-

1.5.11)基础型实验

-

1.5.22)设计型实验

-

1.5.33)综合型实验

-

1.5.44.1 基础型实验

-

1.5.4.14.1.1 门电路的性能测试

-

1.5.4.1.11)实验目的

-

1.5.4.1.22)预习要求

-

1.5.4.1.33)实验内容

-

1.5.4.1.44)实验步骤

-

1.5.4.1.55)实验报告

-

1.5.4.24.1.2 组合逻辑电路逻辑的功能测试

-

1.5.4.2.11)实验目的

-

1.5.4.2.22)预习要求

-

1.5.4.2.33)实验内容

-

1.5.4.2.44)实验步骤

-

1.5.4.2.55)实验报告

-

1.5.4.34.1.3 触发器的组成及集成触发器的性能测试

-

1.5.4.3.11)实验目的

-

1.5.4.3.22)预习要求

-

1.5.4.3.33)实验内容

-

1.5.4.3.44)实验步骤

-

1.5.4.3.55)实验报告

-

1.5.4.44.1.4 典型时序逻辑电路的性能测试

-

1.5.4.4.11)实验目的

-

1.5.4.4.22)预习要求

-

1.5.4.4.33)实验内容

-

1.5.4.4.44)实验步骤

-

1.5.4.4.55)实验报告

-

1.5.4.54.1.5 波形产生和整形电路的应用

-

1.5.4.5.11)实验目的

-

1.5.4.5.22)预习要求

-

1.5.4.5.33)实验内容

-

1.5.4.5.44)实验步骤

-

1.5.4.5.55)实验报告

-

1.5.4.64.1.6 A/D和D/A转换器的应用

-

1.5.4.6.11)实验目的

-

1.5.4.6.22)预习要求

-

1.5.4.6.33)实验内容

-

1.5.4.6.44)实验步骤

-

1.5.4.6.55)实验报告

-

1.5.54.2 设计型实验

-

1.5.5.14.2.1 组合逻辑电路的设计

-

1.5.5.1.11)实验目的

-

1.5.5.1.22)预习要求

-

1.5.5.1.33)实验内容

-

1.5.5.1.44)实验步骤

-

1.5.5.1.55)实验报告

-

1.5.5.24.2.2 时序逻辑电路的设计

-

1.5.5.2.11)实验目的

-

1.5.5.2.22)预习要求

-

1.5.5.2.33)实验内容

-

1.5.5.2.44)实验步骤

-

1.5.5.2.55)实验报告

-

1.5.64.3 综合型实验

-

1.5.6.14.3.1 计数、译码、显示电路

-

1.5.6.1.11)实验目的

-

1.5.6.1.22)预习要求

-

1.5.6.1.33)实验内容

-

1.5.6.1.44)实验步骤

-

1.5.6.1.55)实验报告

-

1.5.6.24.3.2 汽车尾灯显示电路

-

1.5.6.2.11)实验目的

-

1.5.6.2.22)预习要求

-

1.5.6.2.33)实验内容

-

1.5.6.2.44)实验步骤

-

1.5.6.2.55)实验报告

-

1.5.6.34.3.3 竞赛抢答器电路

-

1.5.6.3.11)实验目的

-

1.5.6.3.22)预习要求

-

1.5.6.3.33)实验内容

-

1.5.6.3.44)实验步骤

-

1.5.6.3.55)实验报告

-

1.65 现代数字逻辑系统的设计方法

-

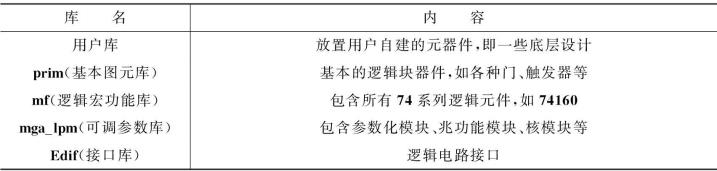

1.6.15.1 可编程逻辑器件简介

-

1.6.25.2 CPLD/FPGA开发环境之一——Max+plusⅡ

-

1.6.2.15.2.1 Max+plusⅡ概述

-

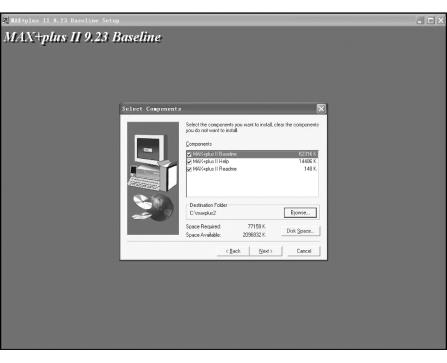

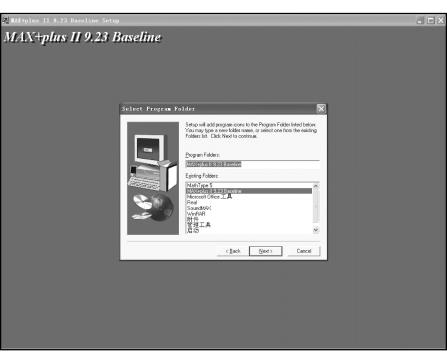

1.6.2.25.2.2 Max+plusⅡ 的安装、设置

-

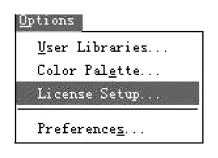

1.6.2.35.2.3 Max+plusⅡ的License设置

-

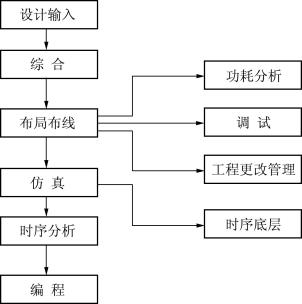

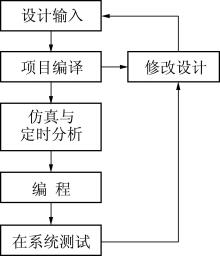

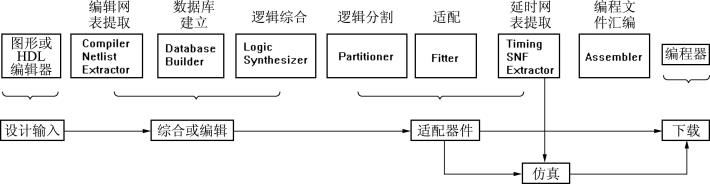

1.6.2.45.2.4 Max+plusⅡ的设计流程

-

1.6.2.4.11)设计输入

-

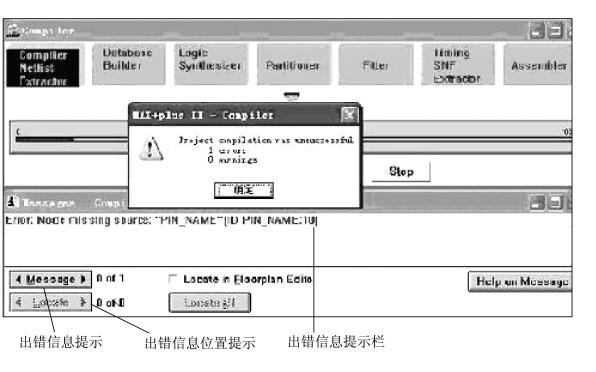

1.6.2.4.22)项目编译

-

1.6.2.4.33)项目校验

-

1.6.2.4.44)器件编程

-

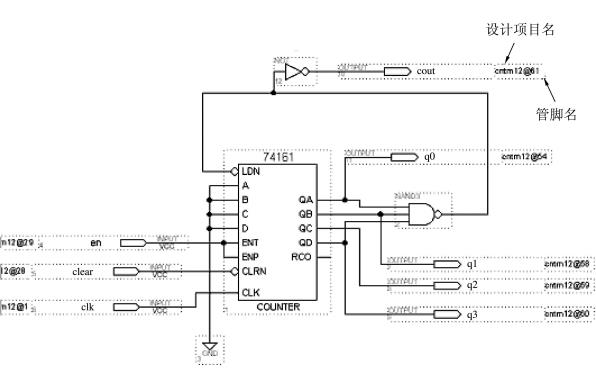

1.6.2.55.2.5 图形输入法的设计过程

-

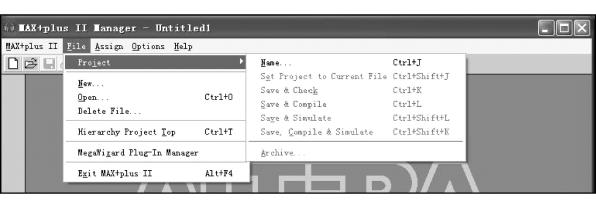

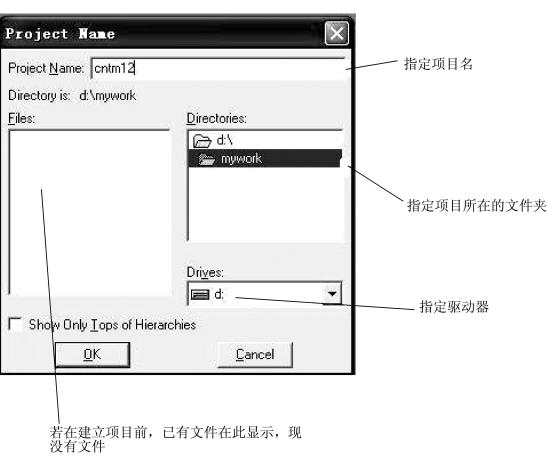

1.6.2.5.11)项目建立

-

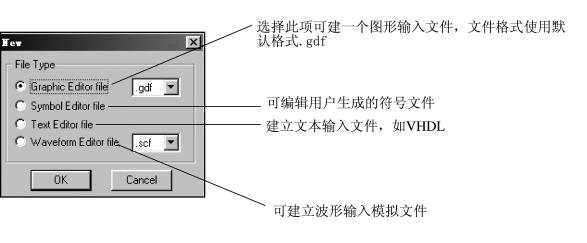

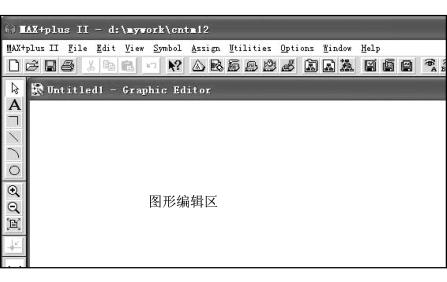

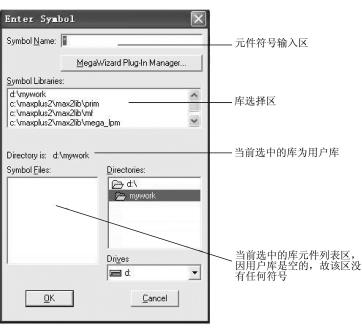

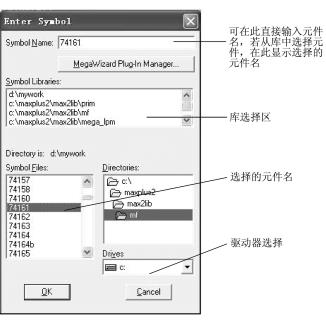

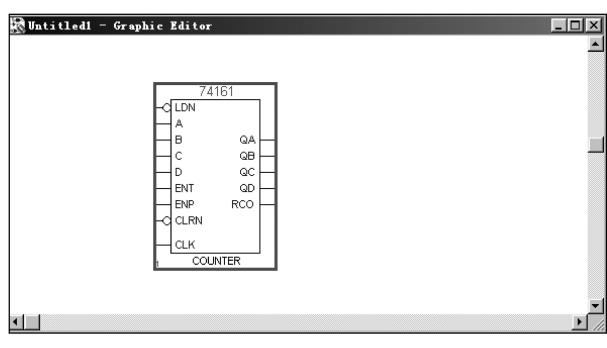

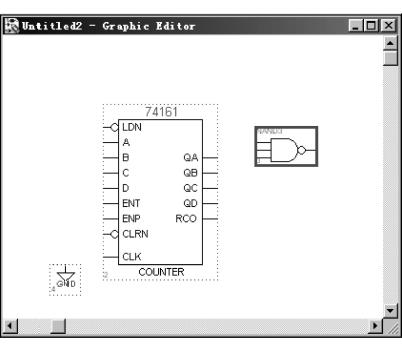

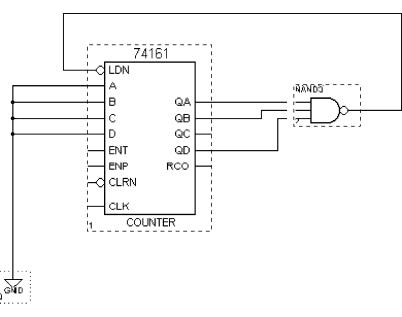

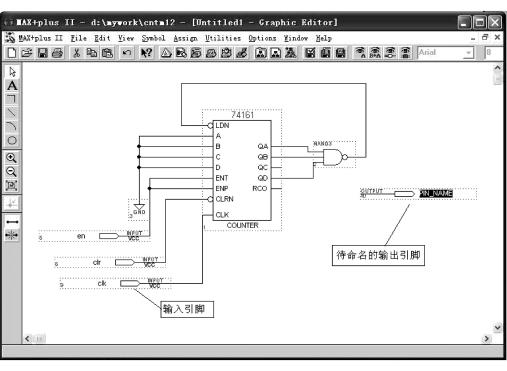

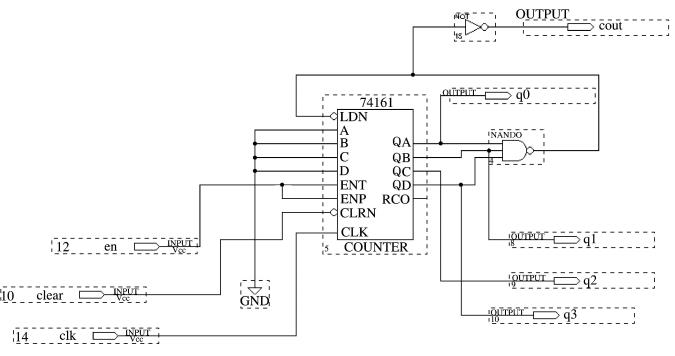

1.6.2.5.22)图形输入

-

1.6.2.5.33)编辑电路原理图

-

1.6.2.65.2.6 项目编译

-

1.6.2.75.2.7 项目校验

-

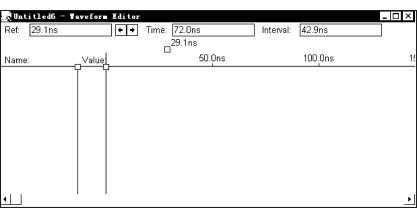

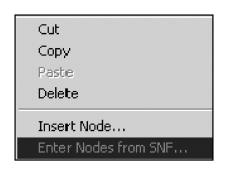

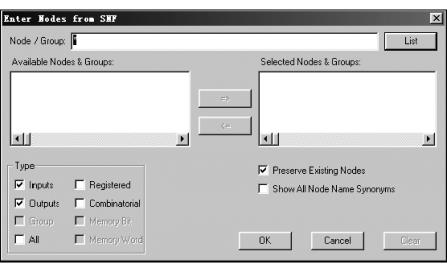

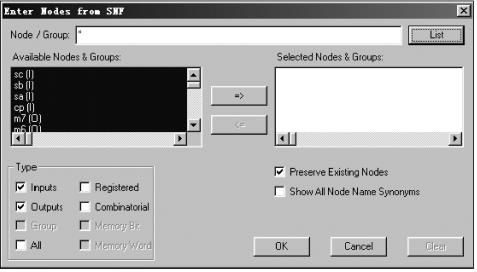

1.6.2.7.11)建立仿真通道文件

-

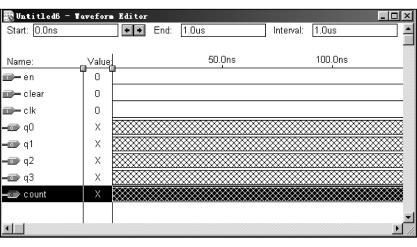

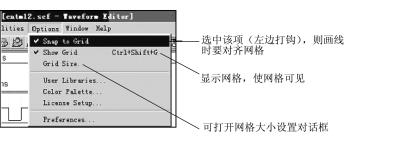

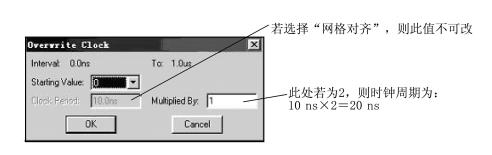

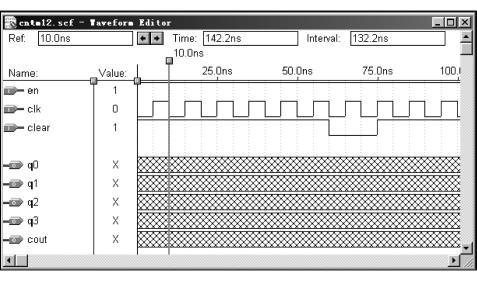

1.6.2.7.22)仿真通道文件的编辑

-

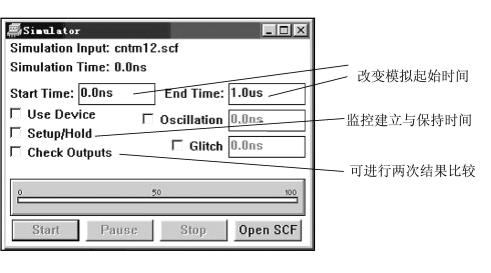

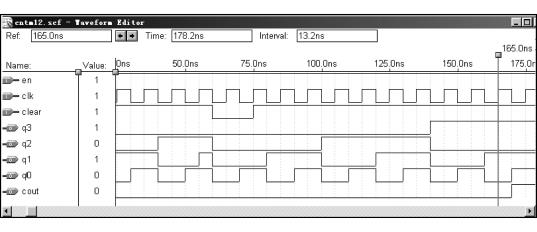

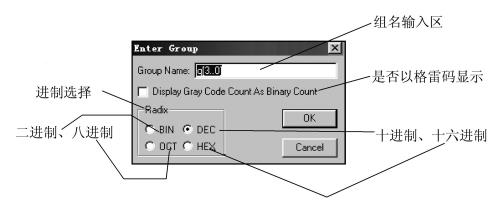

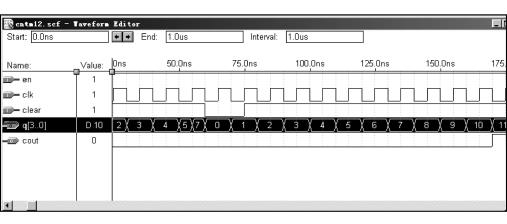

1.6.2.7.33)设计项目的仿真

-

1.6.2.7.44)仿真结果分析

-

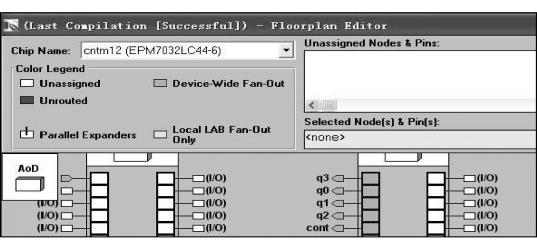

1.6.2.85.2.8 器件编程

-

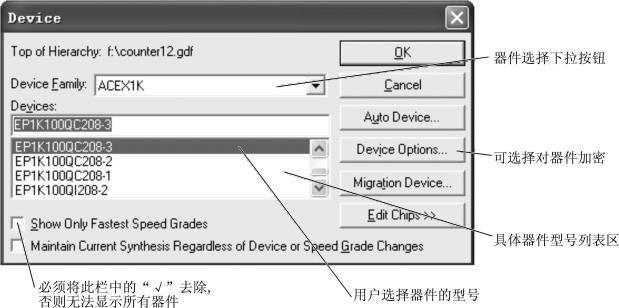

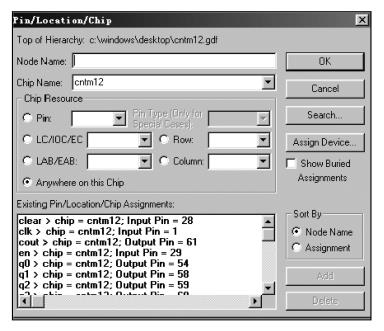

1.6.2.8.11)选择器件

-

1.6.2.8.22)管脚锁定

-

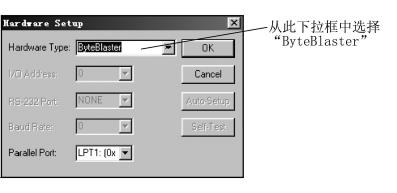

1.6.2.95.2.9 器件编程/配置

-

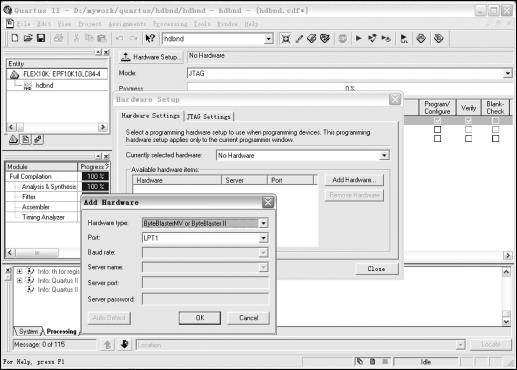

1.6.2.9.11)设置硬件编程/配置

-

1.6.2.9.22)创建编程器日志文件

-

1.6.2.9.33)器件配置

-

1.6.2.105.2.10 单元练习

-

1.6.35.3 常用工具介绍

-

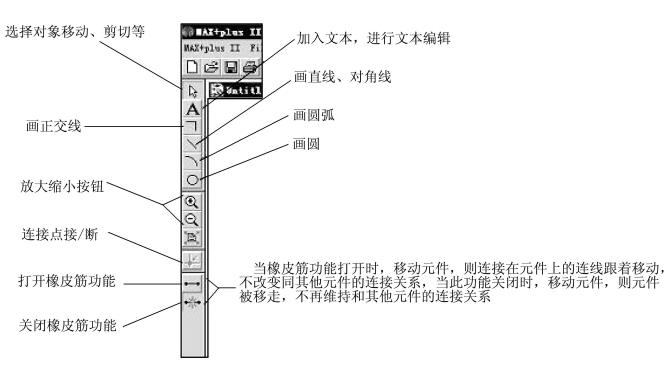

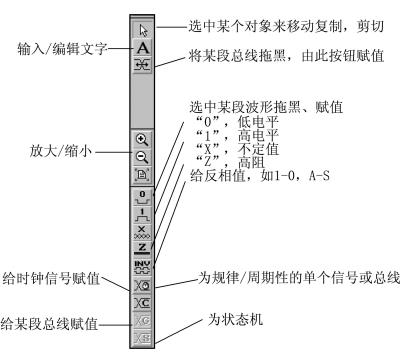

1.6.3.11)工具条简介

-

1.6.3.22)定时分析

-

1.6.45.4 层次化设计及总线

-

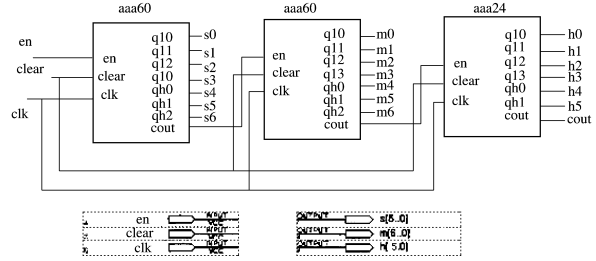

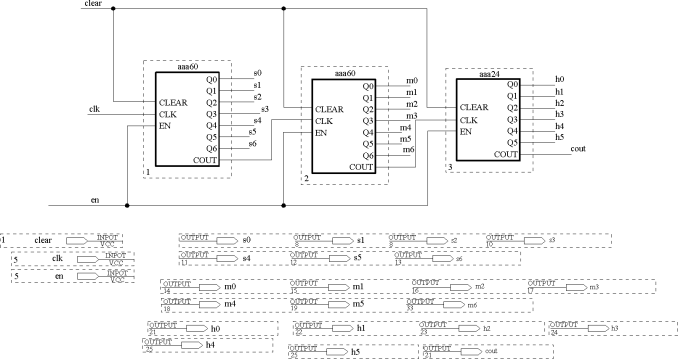

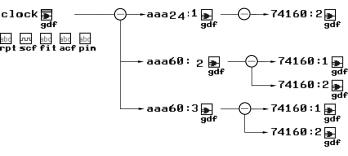

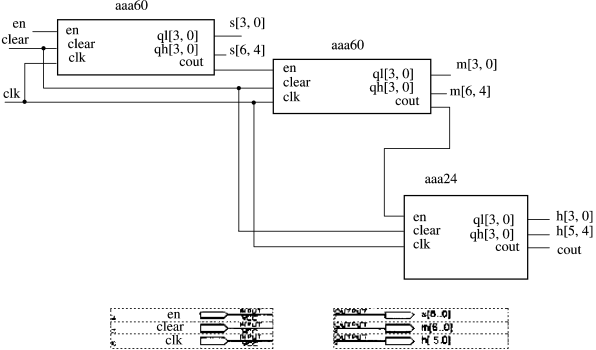

1.6.4.15.4.1 Max+plusⅡ层次化设计

-

1.6.4.1.11)用层次化设计方法设计一个数字钟

-

1.6.4.1.22)层次化设计的注意事项

-

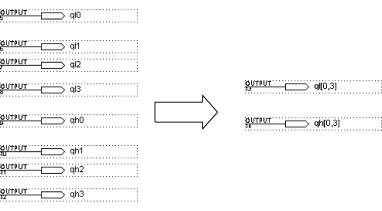

1.6.4.25.4.2 BUS(总线)

-

1.6.4.35.4.3 其他输入法

-

1.6.4.3.11)文本输入法

-

1.6.4.3.22)波形输入法

-

1.6.4.3.33)混合设计输入法

-

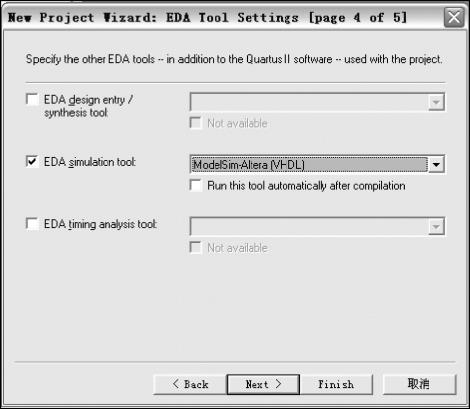

1.6.55.5 CPLD/FPGA开发软件之二——Quartus Ⅱ

-

1.6.5.15.5.1 Quartus Ⅱ简介

-

1.6.5.25.5.2 Quartus Ⅱ使用方法

-

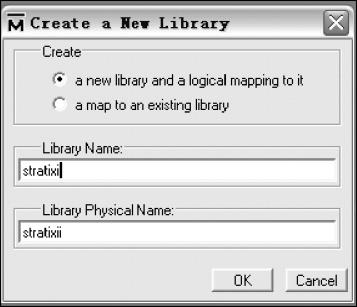

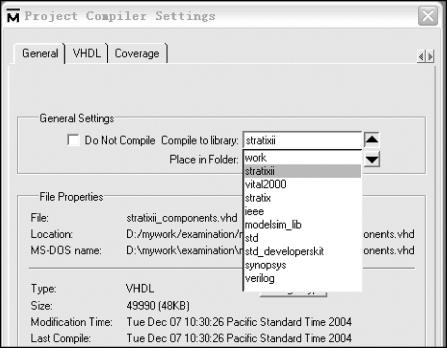

1.6.5.2.11)在Quartus Ⅱ软件中建立项目

-

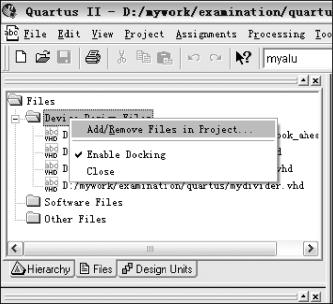

1.6.5.2.22)添加设计输入

-

1.6.5.2.33)编译

-

1.6.5.2.44)静态时序分析

-

1.6.5.2.55)进行仿真

-

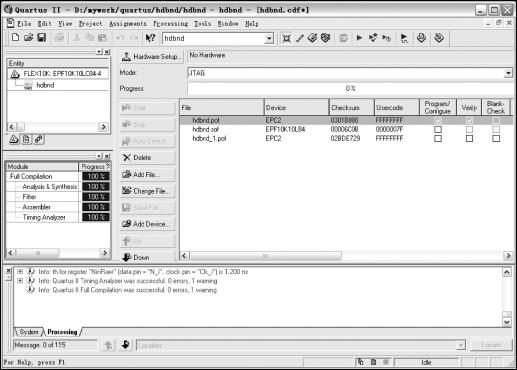

1.6.5.2.66)编程下载

-

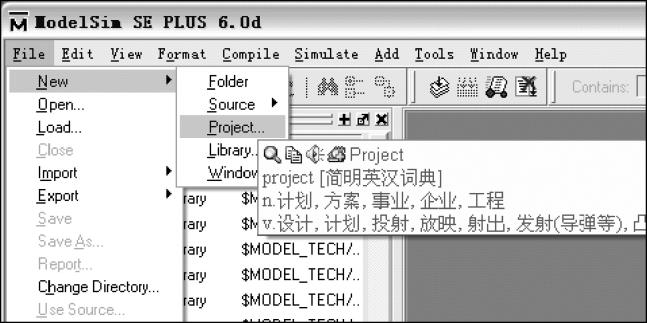

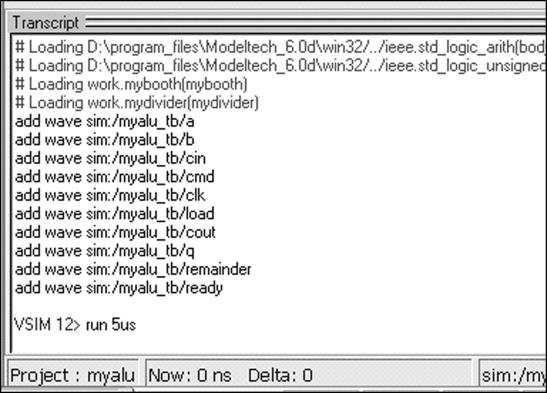

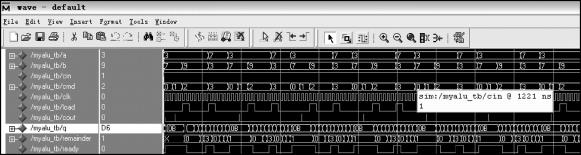

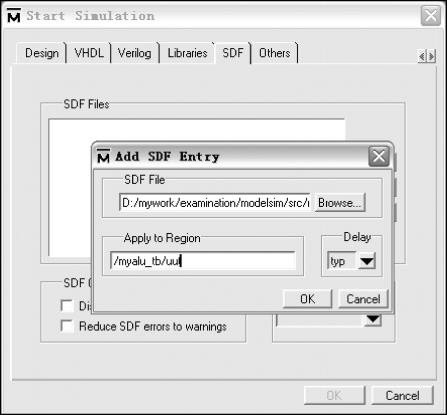

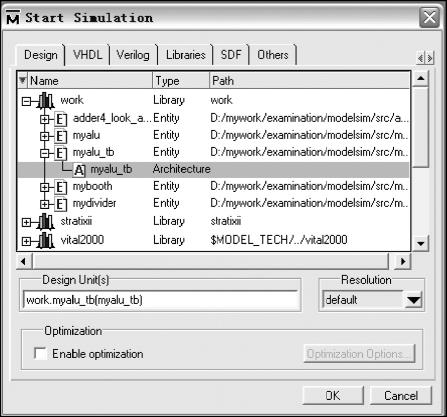

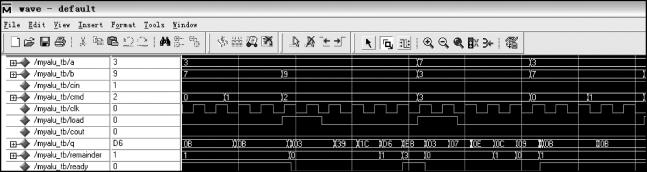

1.6.5.2.77)利用Modelsim进行功能仿真

-

1.6.5.2.88)利用Modelsim进行时序仿真

-

1.6.5.35.5.3 Max+plus Ⅱ与Quartus Ⅱ的功能比较与转换

-

1.76 数字电路课程设计任务

-

1.7.11)数字系统设计方法简介

-

1.7.22)数字逻辑(电路)课程设计的目的

-

1.7.33)课程设计的一般步骤及要求

-

1.7.44)课程设计的时间安排

-

1.7.55)课程设计任务类型

-

1.7.66.1 功能扩展型设计任务

-

1.7.6.16.1.1 声光显示智力抢答器电路的设计

-

1.7.6.1.11)设计目的

-

1.7.6.1.22)电路原理与参考电路

-

1.7.6.1.33)课程设计任务

-

1.7.6.1.44)设计提示

-

1.7.6.26.1.2 彩灯循环显示控制电路的设计

-

1.7.6.2.11)设计目的

-

1.7.6.2.22)电路原理与参考电路

-

1.7.6.2.33)课程设计任务

-

1.7.76.2 综合型设计任务

-

1.7.7.16.2.1 交通灯控制电路

-

1.7.7.1.11)电路原理框图与各模块参考电路

-

1.7.7.1.22)课程设计任务

-

1.7.7.1.33)设计提示

-

1.7.7.26.2.2 多功能数字钟

-

1.7.7.2.11)原理框图与各功能模块的参考电路

-

1.7.7.2.22)课程设计任务

-

1.7.7.2.33)设计提示

-

1.7.86.3 创新设计电路

-

1.7.8.16.3.1 电子密码锁的设计(一)

-

1.7.8.1.11)原理框图与各功能模块

-

1.7.8.1.22)课程设计任务

-

1.7.8.1.33)设计提示

-

1.7.8.26.3.2 电子密码锁的设计(二)

-

1.7.8.2.11)原理框图及各功能模块(见图6.3.2)

-

1.7.8.2.22)课程设计任务

-

1.7.8.2.33)设计提示

-

1.7.8.36.3.3 出租车自动计费电路

-

1.7.8.3.11)设计原理及框图

-

1.7.8.3.22)课程设计任务

-

1.7.8.3.33)设计提示

-

1.7.8.46.3.4 汽车尾灯控制器

-

1.7.96.4 自行选题

-

1.7.9.16.4.1 拔河游戏机

-

1.7.9.1.11)设计任务

-

1.7.9.1.22)设计提示

-

1.7.9.26.4.2 电话键显示电路

-

1.7.9.2.11)设计任务

-

1.7.9.2.22)设计提示

-

1.7.9.36.4.3 量程可变的频率计

-

1.7.9.3.11)设计任务

-

1.7.9.3.22)设计提示

-

1.7.9.46.4.4 洗衣机控制电路

-

1.7.9.4.11)设计任务

-

1.7.9.4.22)设计提示

-

1.7.9.56.4.5 电梯控制器

-

1.7.9.5.11)设计任务

-

1.7.9.5.22)设计提示

-

1.8附录

-

1.9参考文献

1

数字电子技术实验与课程设计指导

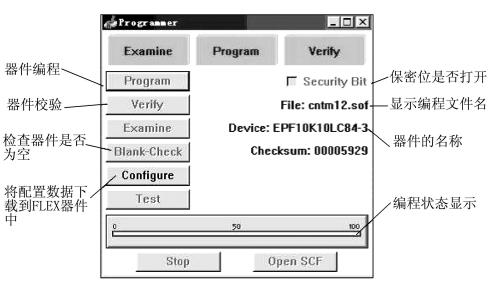

”按钮可打开编程器对话框,如图5.2.39所示。

”按钮可打开编程器对话框,如图5.2.39所示。