数字电路应用广泛,Simulink为数字电路仿真提供了基本的逻辑运算模块和多种触发器模块。

组合逻辑电路在任何给定时刻的输出值仅仅与该时刻电路的输入值有关,而与过去的输入状态无关。常用的组合逻辑电路有半加器、全加器、比较器、编码器、译码器等等。下面通过实例介绍在Simulink中如何进行组合逻辑电路仿真。

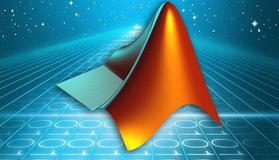

[例6-6]仿真实现3-8译码器。

根据以上分析内容搭建仿真模型,模型文件中的模块主要有:脉冲序列发生器模块、逻辑操作模块。

(1) 利用脉冲序列发生器(Pulse Generator)仿真产生,Pulse Generator位于 Sources库中,用于产生所需的原始脉冲序列。参数设置窗口如图6-12所示。选择“Pulsetype”为“Samplebased”,参数中Period用于设定以采样时间为单位的脉冲序列周期,Pulse width 用于设定以采样时间为单位,每个脉冲持续的时间长短,即正脉宽,Phasedelay(number ofsamples),用于设定每个脉冲的相位延迟时间,同样以采样时间为单位。在本例设置,Period设置为2,即周期是2个采样时间长度。Pulse width 设置为1,

利用脉冲序列发生器(Pulse Generator)仿真产生,Pulse Generator位于 Sources库中,用于产生所需的原始脉冲序列。参数设置窗口如图6-12所示。选择“Pulsetype”为“Samplebased”,参数中Period用于设定以采样时间为单位的脉冲序列周期,Pulse width 用于设定以采样时间为单位,每个脉冲持续的时间长短,即正脉宽,Phasedelay(number ofsamples),用于设定每个脉冲的相位延迟时间,同样以采样时间为单位。在本例设置,Period设置为2,即周期是2个采样时间长度。Pulse width 设置为1, 采样时间(Sample time)可依次设置为1、2、4。

采样时间(Sample time)可依次设置为1、2、4。

图6-12Pulse Generator参数设置窗口

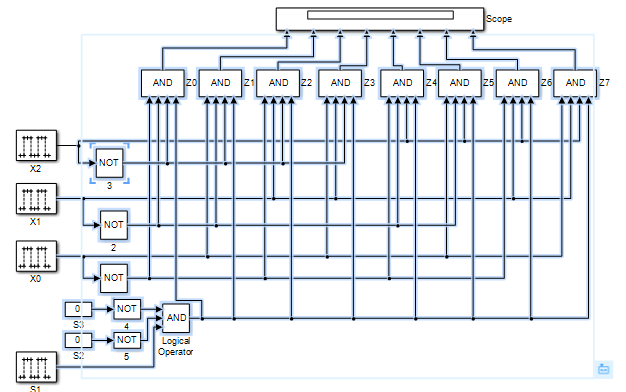

(2)逻辑表达式运算应用Logical Operator模块实现,Logical Operator位于Simulink库下的Logic and bit Operations子库中,其参数设置中,“Operator”下拉列表框用于设置模块要实现的逻辑功能,包括与、或、与非、或非、异或、非等六项逻辑运算表达形式。设置完成,搭建模型如图6-13所示。

图6-13 3-8译码器仿真模型

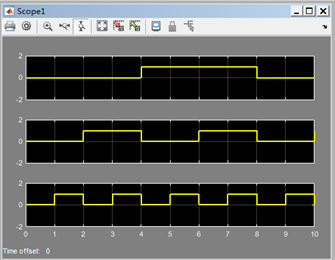

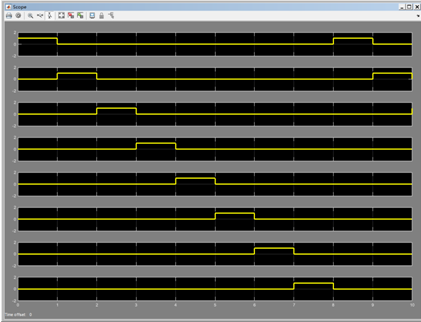

在模型仿真参数设置中,仿真终止时间设置为10,进行仿真。仿真完成后,双击示波器观察,输入信号仿真结果如图6-14所示,仿真输出结果如图6-15所示。

图6-14 译码器输入仿真结果图

图6-153-8译码器输出仿真结果图

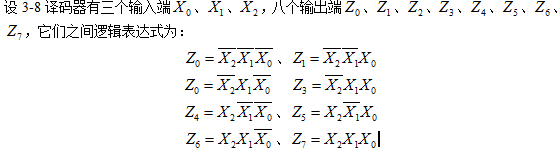

[例6-7]仿真实现4-16译码器。

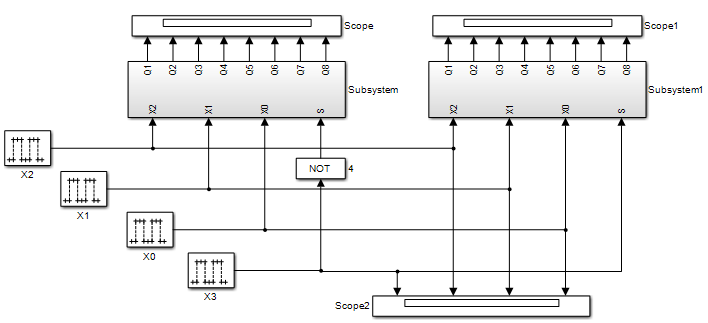

4-16译码器仿真可以采用类似3-8译码器的方法进行。也可以利用已封装的带使能端的3-8译码器来搭建,下面介绍后一种方法。

(1)修改图6-13所示的3-8译码器仿真模型,增加S1、S2、S3三个控制端,当S2、S3低电平,S1接高电平时,译码器工作。

图6-16 增加控制端的3-8译码器仿真模型

(2)用鼠标选择圈定要封装的范围,单击鼠标右键,在弹出的菜单中,选择“CreateSubsystem from Selecttion”,建立子系统。

(3)应用所生成子系统搭建4-16译码器,并修改端口名称。

图6-17 4-16译码器仿真模型