目 录

3.1. 印制电路板(PCB-printed circuit board)

3.12. 金属化孔(platedthrough hole)

3.13. 非金属化孔(NPTH—unsupported hole)

3.17. HDI (High DensityInterconnect)

3.19. 阻焊膜(soldermask or solder resist)

3.21. 双列直插式封装 (DIP—dual-in-line package)

3.22. 单列直插式封装 (SIP—single-inline package)

3.23. 小外型集成电路 (SOIC—small-outline integrated circuit)

3.25. THT(Through Hole Technology)

3.26. SMT (Surface Mounted Technology)

3.34. 立片(器件直立,Tombstonedcomponent)

3.36. 反标注(反向标注,Backannotation)

3.38. 材料清单(BOM-Bill of materials)

3.40. 设计规则检查(DRC-Design rules checking)

3.41. DFM(Design ForManufacturability)

3.42. DFT(Design ForTestability)

3.44. EMC(Electromagnetic compatibility)

6.9.3. 有隔离变压器的接口(E1/T1口和类似端口)的安规要求

印制电路板(PCB)设计规范

本规范规定了我司硬件工程师在CAD/SI开发阶段参与产品的设计过程和必须遵守的设计原则。

本规范适用于我司硬件工程师在CAD/SI阶段设计生产的所有印制电路板(简称PCB)。

下列文件中的条款通过本规范的引用而成为本规范的条款。凡是注日期的引用文件,其随后所有的修改单(不包括勘误的内容)或修订版均不适用于本规范,然而,鼓励根据本规范达成协议的各方研究是否可使用这些文件的最新版本。凡是不注日期的引用文件,其最新版本适用于本规范。

| 序号 | 编号 | 名称 |

| 1 | GB4588.3—88 | 印制电路板设计和使用 |

3.1. 印制电路板(PCB-printed circuit board)

在绝缘基材上,按预定设计形成印制器件或印制线路以及两者结合的导电图形的印制板。

电路原理图,用原理图设计工具绘制的、表达硬件电路中各种器件之间的连接关系的图。

由原理图设计工具自动生成的、表达元器件电气连接关系的文本文件,一般包含元器件封装、网络列表和属性定义三部分。

用于互连更小的单板的电路板。

封装和互连结构的一面,该面在布设总图上就作了规定(通常此面含有最复杂的或多数的元器件。此面在通孔插装技术中有时称做“元器件面”)。

封装及互连结构的一面,它是TOP面的反面。(在通孔插装技术中此面有时称做“焊接面”)。

pitch≤0.65mm的翼形引脚器件;

pitch≤1.0mm的面阵列器件。

器件安装在PCB上后,本体底部与PCB表面的距离。

和长针的背板连接器配合使用,安装在连接器的另一面,保护连接器的插针。

单板插入到背板上,从插板方向看,PCB 在右边,器件面在左边。

包括导电层在内的包覆金属基材板的厚度。板厚有时可能包括附加的镀层和涂敷层。

3.12. 金属化孔(plated through hole)

孔壁镀覆金属的孔。用于内层和外层导电图形之间的连接。同义词:镀覆孔

3.13. 非金属化孔(NPTH—unsupported hole)

没有用电镀层或其他导电材料加固的孔。

用作贯通连接的金属化通孔,内部不需插装器件引脚或其他加固材料。

来自TOP面或BOTTOM面,而不穿过整个印制电路板的过孔。

完全被包在板内层的孔。从任何表面都不能接近它。

3.17. HDI (High Density Interconnect)

高密度互连。

在焊盘上的过孔或盲孔。

3.19. 阻焊膜(solder mask or solder resist)

是用于在焊接过程中及焊接之后提供介质和机械屏蔽的一种覆膜。阻焊膜的材料可以采用液体的或干膜形式。

用于电气连接、器件固定或两者兼备的部分导电图形。

3.21. 双列直插式封装 (DIP—dual-in-line package)

一种元器件的封装形式。两排引线从器件的侧面伸出,并与平行于元器件本体的平面成直角。

3.22. 单列直插式封装 (SIP—single-inline package)

一种元器件的封装形式。一排直引线或引脚从器件的侧面伸出。

3.23. 小外型集成电路 (SOIC—small-outline integrated circuit)

球栅阵列封装器件。指在元件底部以矩阵方式布置的焊锡球为引出端的面阵式封装集成电路。目前有塑封BGA(P-BGA)和陶瓷封装BGA(C-BGA)两种。焊锡球中心距有1.5 mm,1.27 mm,1 mm,0.8 mm,0.65mm,0.5mm,0.4mm。

3.25. THT(Through Hole Technology)

通孔插件技术。

3.26. SMT (Surface Mounted Technology)

表面安装技术。

为压入金属化孔且不需要额外焊接而设计的具有专门形状截面的插针。

印制板与连续循环的波峰状流动焊料接触的焊接过程。

是一种将零、部件的焊接面涂覆焊料后组装在一起,加热至焊料熔融,再使焊接区冷却的焊接方式。

由弹性的可变形的插针,或实体(刚性)的插针与PCB的金属化孔配合而形成的一种连接。在插针与金属化孔之间形成紧密的接触点。

导线之间由焊料形成的多余导电通路。

焊料在层压板、阻焊层或导线表面形成的小球(一般发生在波峰焊或再流焊之后)。

3.33. 锡尖(拉尖,solder projection)

出现在凝固的焊点上或涂覆层上的多余焊料凸起物。

3.34. 立片(器件直立,Tombstoned component)

一种缺陷,无引线器件只有一个金属化焊端焊在焊盘上,另一个金属化焊端翘起,没有焊在焊盘上。

当前正在编辑的层。当前层与辅助层配对。

3.36. 反标注(反向标注,Back annotation)

根据PCB设计文件中所作的改动更新原理图文件,通常采用程序进行执行完成此项工作。在更换管脚、更换门、参考标号重新编号以后必须进行反标注。

在PCB layout过程中,FANOUT指的是扇出打孔。即从焊盘处引短线打孔,分为自动和手动两种。

3.38. 材料清单(BOM-Bill of materials)

装备部件的格式化清单。

由绘图仪产生电路板工艺图的过程,绘图仪使胶片曝光从而将被绘制部分制成照片。

3.40. 设计规则检查(DRC-Design rules checking)

通过通知您设计违规,确保建立的设计符合规定的设计规则的程序。

3.41. DFM(Design For Manufacturability)

可制造性设计。

3.42. DFT(Design For Testability)

可测试性设计。

在线测试,也称内电路测试,即采用隔离技术,在被测PCB上的测试点施加测试探针来测试器件、电路网络特性的一种电性能测试方法。

3.44. EMC(Electromagnetic compatibility)

电磁兼容。设备或系统在其电磁环境中能正常工作且不对该环境中任何事物构成不能承受的电磁骚扰的能力(ANSI C64.14-1992)。

信号完整性。

电源完整性。

CAD/SI开发人员的活动贯穿于整个产品开发过程中,为产品开发提供全流程的信号完整性分析、布局布线设计、测试验证等系统和单板物理设计与实现方面的技术服务。

CAD/SI开发人员参与产品的活动过程分为四个阶段:

CAD/SI系统分析过程;

前仿真及布局过程;

布线及仿真验证过程;

测试验证过程。

4.1. 系统分析

硬件工程师在CAD/SI阶段根据总体框架,对系统高速互连进行信号完整性分析,确定系统框架分割的合理性。其内容涉及系统互连设计,单板关键总线的信噪和时序分析,关键元器件的应用分析及选型建议,物理实现关键技术分析等内容。

4.2. 布局

在综合考虑信号质量、EMC、热设计、DFM、DFT、结构、安规等方面要求的基础上,将器件合理的放置到板面上。

4.3. 仿真

在器件IBIS、SPICE 等模型的支持下,利用EDA工具对PCB的预布局、布线进行信号质量和时序分析,得出一定的物理电气规则参数,并运用于布局布线中,从而在单板的物理实现之前解决PCB设计中存在的时序问题和信号完整性问题。仿真通常分为前仿真分析和后仿真验证两部分。

4.4. 布线

在遵循信号质量、DFM、EMC等规则要求下,实现器件管脚间的物理连接设计。

4.5. 测试验证

硬件工程师在CAD/SI阶段从PCB物理实现的角度参与硬件测试中的信号完整性测试部分,进行信号质量和时序测试,并对出现的信号质量问题进行处理。测试验证主要涉及信号质量测试、信号时序测试和容限测试等三个方面工作。

5.1. 系统框架划分

在硬件系统方案中,根据系统的功能模块对系统框架进行了划分。这里,我们从CAD/SI的实现角度,对其框架划分方案进行验证。若验证后发现有不合理的地方,应给出解决方法,提出合理的框架划分方案。

对于大部分已经有继承性的产品来说,其系统各功能模块的划分已经过相关产品的验证,这时可省略这部分的分析内容。这里单独提出这一部分的分析要求,主要针对部分新产品,尤其是预研产品,由于新技术或新方案中选用的套片或部分芯片使用了较新的接口、电平类型或封装,须结合有关技术资料,从CAD设计实现和SI仿真方面进行分析。

分析时首先要对当前硬件总体划分的模块中涉及的总线及电平特点,该总线的驱动负载能力,多负载情况下的信号完整性问题等进行分析阐述,论证系统框架划分是否合理,若不合理,给出推荐的划分方案和分析数据。其次,若系统中有器件密度及可能布线密度较大的单板,需要分析其信号完整性问题和PCB实现难度等,通过分析论证这种划分的合理性。

5.2. 系统互连设计

系统互连有框间互连、板间互连、模块间互连三种形式,可根据具体情况进行分析。分析要点如下:

Ø 分析系统互连的电平的特点,使用中的匹配方式,若同一种接口电平不同厂家不同器件的性能差别明显,应给出优选方案;

Ø 若互连采用的是同步或准同步总线需要进行静态时序分析;

Ø 对多负载网络需要根据不同的拓扑结构给出仿真波形;

Ø 点到点结构的网络可酌情给出不同匹配情况的仿真波形;

Ø 对信号排布较密或对串扰敏感的电平需要给出信号在连接器上不同排布情况下的串扰仿真分析;

Ø 根据仿真波形给出噪声裕量分析。

5.3. 单板关键总线的信噪和时序分析

对系统的关键单板需要进行重点分析,分析要点有两个:总线信噪分析和时序分析。

Ø 信噪分析主要是串扰分析。

首先确定信号电平的直流噪声容限,分析当器件工作在最坏情况下时,对关键总线在不同线宽/线间距时的串扰进行分析,综合设计难度、加工难度等因素,在满足直流噪声容限的情况下,确定PCB实现的线宽/线间距约束条件。

Ø 时序分析。

这里指静态时序分析。根据单板中时钟的同步方式,用计算静态时序的方法,计算出关键总线的PCB传输延迟,从而得出各接口间的PCB走线长度。

5.4. 关键元器件的选型建议

从信号质量、封装、时序等方面进行分析:

Ø 从信号完整性分析的角度,分析相同功能的不同器件,在相同的工作条件下,根据仿真波形,根据信号质量的不同,给出优选器件。对于只有一种器件的情况,也可仿真出不同条件下(高、低温,单负载或多负载等)的信号波形,分析其接口性能,给出该器件是否满足系统要求的选型建议。

Ø 若同一器件有多种封装,应该结合当前我们的供应商的技术水平和我们生产的工艺水平,选择易于设计和实现的PCB封装形式,给出选型建议。

5.5. 物理实现关键技术分析

物理实现即PCB设计实现方案。根据系统中不同的信号特性,可选择从如下几个方面进行分析。

Ø 当系统中有高速总线时,如果需要在PCB板上传输较长的距离,且收发器对传输中的信号抖动、损耗有严格要求;或者信号要求有较高的传输线特征阻抗,预计用普通FR4材料设计单板将严重超出结构要求的厚度。这时可考虑使用低损耗、低介电常数的材料。

Ø 若预测单板布线密度很大,采用常规的通孔设计方法无法在有限的PCB信号层内完成布线时,可考虑使用埋盲孔设计方法或采用HDI设计及加工方法等。但是,是否采用这种方法需要与中试单板工艺、采购等专家进行研究协商,综合成本和生产加工等因素再决定。因为,由于目前国内PCB加工厂家的加工工艺有限,同时我们的测试手段也受限制,所以采用埋盲孔和HDI设计的单板,加工直通率相对较低,若预计今后单板批量生产量较大时,应尽量避免使用这些非常规设计方法。

6.1. 理解设计要求并制定设计计划

Ø 仔细审读原理图和功能框图,在与原理图设计者充分交流的基础上,确认PCB设计的电气性能要求。

Ø 制定单板的PCB设计计划,填写设计记录表,计划要包含设计过程中原理图调入、预布局、仿真分析、布局完成、布局评审、布线完成、布线评审、等关键检查点的时间要求。如果出现由于种种原因导致设计计划推迟的情况,要制定相应的调整计划,而且需注明原因并由相关人员签字确认。

6.2. 创建网络表和板框

Ø 对于改板、归档或套用板框的PCB文件必须从文档室申请。

Ø 对原理图的规范性进行检查,积极排除错误,保证网络表的正确性和完整性。

Ø 根据器件编码与封装对应相关数据库确定器件的封装。

Ø 根据原理图和PCB设计工具的特性,选用正确的网络表格式,创建符合要求的网络表。

Ø 根据结构要素图或对应的标准板框,创建PCB设计文件。 坐标原点必须为选择单板左边、下边的延长线交汇点。

Ø 板框四周倒圆角,圆角半径5mm/197mil。特殊情况参考结构设计要求。

6.3. 预布局

Ø 参考原理图和功能框图根据信号流向放置重要的单元电路和核心器件。

Ø 对关键信号进行前仿真分析。仿真分析方法详见本规范6.5章节的信号质量。

Ø 根据仿真分析结果来确定重要单元电路和核心器件的大概布局位置,使关键信号能够满足时序和信号质量等要求。

6.4. 布局的基本原则

Ø 与相关人员沟通以满足结构、SI、DFM、DFT、EMC方面的特殊要求。

Ø 根据结构要素图,放置接插件、安装孔、指示灯等需要定位的器件,并给这些器件赋予不可移动属性,并进行尺寸标注。

Ø 根据结构要素图和某些器件的特殊要求,设置禁止布线区、禁止布局区域。

Ø 综合考虑PCB性能和加工的效率选择工艺加工流程(优先为单面SMT;单面SMT+插件;双面SMT;双面SMT+插件),并根据不同的加工工艺特点布局。

Ø 布局时参考预布局的结果,根据“先大后小,先难后易”的布局原则。

Ø 布局应尽量满足以下要求:总的连线尽可能短,关键信号线最短;高电压、大电流信号与低电压、小电流信号的弱信号完全分开;模拟信号与数字信号分开;高频信号与低频信号分开;高频元器件的间距要充分。在满足仿真和时序分析要求的前提下,局部调整。

Ø 相同电路部分尽可能采用对称式模块化布局。

Ø 布局设置建议栅格为50mil,IC器件布局,栅格建议为2525 25 25 mil。布局密度较高时,小型表面贴装器件,栅格设置建议不少于5mil。

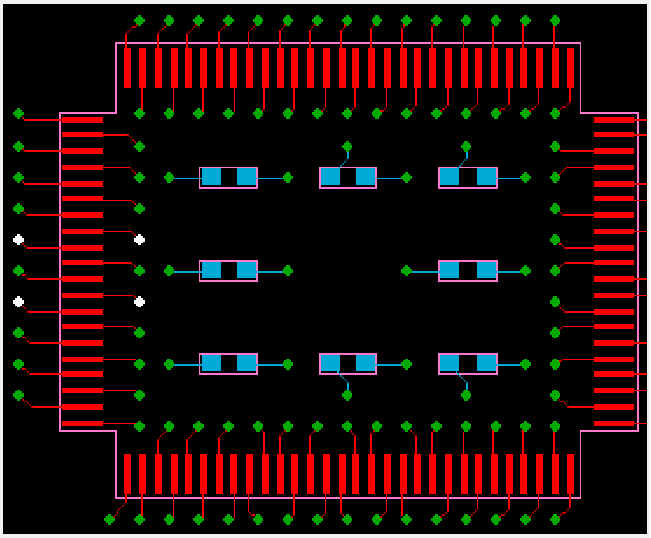

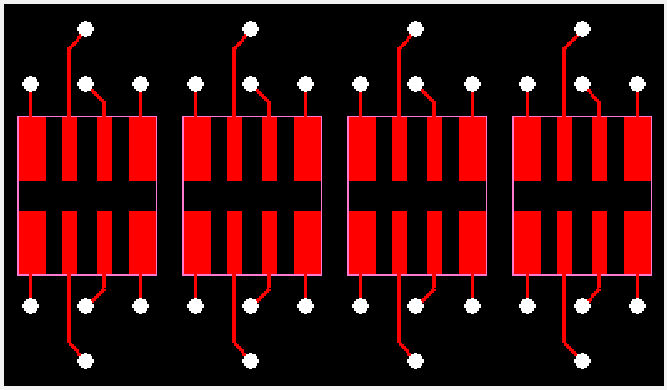

Ø 布局时,考虑fanout和测试点的位置,以器件中心点参考移动,考虑在两个过孔中间走两根走线,如下图6-4-1、图6-4-2所示:

图6-4-1 FANOUT示例1

图6-4-2 FANOUT示例2

测试点ICT的要求详见本规范第6.7章节的DFT设计要求。

Ø 布完局后所有器件必须放置在PCB板内。

Ø 布完局后打印出装配图供原理图设计者检查器件封装的正确性,并且确认单板、背板和接插件的信号对应关系。

Ø 布完局后经评审人员确认无误后方可开始布线。

6.5. 信号质量

假如信号的上升沿时间小于4倍的信号传输延时时,我们可视它为高速信号。这时我们必须用传输线的方法和手段来分析。高速信号的特点要求我们在设计中必须对关键的信号制定约束规则,由约束规则驱动布局布线。

6.5.1. 规则分析

单板的规则分析建立在系统分析的基础之上,在分析单板的设计规则前应先充分了解系统分析报告,掌握单板设计要求,通过对设计要求的分析得到设计规则,利用设计规则驱动单板布局和布线。

单板规则分析可以分为以下几个部分。

Ø 时序计算

满足建立时间和保持时间是时序电路的基本要求。时序计算的基本公式如下:

Tpropmax=Tcycle - Tmin_setup - Tmax_out_valid +/- Tskew- Tjitter - Tcrosstalk

Tpropmin=Tmin_in_hold - Tout_hold +/- Tskew + Tjitter+ Tcrosstalk

其中:

Tpropmax为传输线允许的最大传输延时;

Tpropmin为传输线允许的最小传输延时;

Tcycle为时钟周期; Tmin_setup为输入器件的最小建立时间;

Tmax_out_valid为输出器件的最大输出有效时间,有的资料定义为Tco,其含义为时钟边沿到达到有效数据输出所需要的一段时间差;

Tskew为输入输出器件时钟输入PIN处的相对延时,即时钟相差;

Tjitter 为时钟抖动引入的延时,这种延时可能造成时钟周期的变化;

Tcrosstalk为总线的同步串扰引入的延时;

Tmin_in_hold为输入器件的最小保持时间;

Tout_hold为输出器件的输出保持时间。

在器件的数据手册中可得到相关的参数,通常Tjitter+Tcrosstalk近似为0.5ns。通过计算可得到传输线允许的最大传输延时,最小传输延时。

通过静态时序分析可以对芯片的器件选型以及布局布线进行指导,一般的地,建立时间的要求决定了同步电路传输线的最大走线长度,而保持时间的要求决定了同步电路传输线的最小走线长度,器件的建立和保持时间是针对输入信号的器件而言的。

Ø 关键网络拓扑分析

关键网络拓扑分析包含了多负载网络的拓扑结构和网络匹配方式分析。

多负载拓扑网络的仿真可通过搭建拓扑结构模型,结合器件的基本布局在满足时序的要求下,尝试各种拓扑结构和匹配方式,来确定基本的拓扑类型。如果是BUS总线还要进一步的确定总线间长度的相互关系,并把仿真结果作为布局布线规则输入到软件中,作为规则驱动布局布线的基础。

对于信号是沿有效还是电平有效,在仿真中要区别对待。

Ø 串扰

关键网络的串扰,可通过搭建模型进行仿真,得出满足器件串扰要求的最小信号线间距。

可设网络的间距规则,或设Max Parallelism(信号线平行多长的则间距应多大的列表),作为规则输入到软件中。

Ø 差分线

对于差分结构的网络,需要考虑:

差分阻抗(差分线的单线阻抗仅具有参考价值)。通过阻抗计算软件(如:Si8000v3.0)计算可得。

差分线匹配。通过仿真确定匹配值,匹配长度的范围。

与其它网络的间距。为了减少差分线与其它信号的耦合作用,应使差分线对与其他信号线的距离大于差分线间距。

Ø 时钟线

对于时钟线的网络需考虑;

仿真决定匹配方式和阻抗的选取;

时钟线的边沿要单调,边沿满足要求;

满足时钟信号时序(长度)要求。

Ø 其他规则

对于特殊网络的最大最小线宽,间距等要进行特殊规则定义并输入到软件中。其他规则设置参见7. 1的布线的基本要求和7.2的布线约束规则设置。

6.5.2. 层设计与阻抗控制

Ø 层设计

根据单板的电源地的种类、信号密度、板级工作频率、有特殊布线要求的信号数量,以及综合单板的性能指标要求与成本承受能力,确定单板的层数。

1) 电源层和地层

单板电源的层数主要由其种类数量决定的。对于单一电源供电的PCB,一个电源平面足够了;对于多种电源,若互不交错,可考虑采取电源层分割(尽量保证相邻层的关键信号布线不跨分割区);对于电源互相交错的单板,考虑采用2个或以上的电源平面。

对于平面层的设置需满足以下条件:

对不同的电源和地层进行分隔,其分隔宽度要考虑不同电源之间的电位差,电位差大于12V时,分隔宽度为50mil,反之,可选20--25mil。

平面分隔要考虑高速信号回流路径的完整性,相邻层的关键信号不跨分割区。

当高速信号的回流路径遭到破坏时,应当在其他布线层给予补偿。例如可用接地的铜箔将该信号网络包围,以提供信号的地回路。

注意电源与地线层的完整性。对于导通孔密集的区域,要注意避免孔在电源和地层的挖空区域相互连接,形成对平面层的分割,从而破坏平面层的完整性,并进而导致信号线在地层的回路面积增大。

不同电源层在空间上要避免重叠。主要是为了减少不同电源之间的干扰,特别是一些电压相差很大的电源之间,电源平面的重叠问题一定要设法避免,难以避免时可考虑中间隔地层。

20H规则:由于电源层与地层之间的电场是变化的,在板的边缘会向外辐射电磁干扰。称为边沿效应。解决的办法是将电源层内缩,使得电场只在接地层的范围内传导。以一个H(电源和地之间的介质厚度)为单位,若内缩20H则可以将70%的电场限制在接地层边沿内;内缩100H则可以将98%的电场限制在内。

地的层数除满足平面层的要求外,还要考虑:

与器件面相邻层有相对完整的地平面;

高频、高速、时钟等关键信号有一相邻地平面;

关键电源有一对应地平面相邻(如48V与BGND相邻)。

2) 信号层

信号的层数主要由关键信号网络和局部高密度走线决定的。EDA软件能提供一布局、布线密度参数报告,由此参数可对信号所需的层数有个大致的判断,根据以上参数再结合板级工作频率、有特殊布线要求的信号数量以及单板的性能指标要求与成本承受能力,最后确定单板的信号层数。在确定信号的层数时,需考虑关键信号网络(强辐射网络以及易受干扰的小、弱信号)的屏蔽或隔离措施。

3) 层的排布

多层PCB层排布的一般原则:

器件面下面(第二层)为地平面,提供器件屏蔽层以及为器件面布线提供参考平面;

所有信号层尽可能与地平面相邻;

尽量避免两信号层直接相邻;

主电源尽可能与其对应地相邻;

原则上应该采用对称结构设计。对称的含义包括:介质层厚度及种类、铜箔厚度、图形分布类型(大铜箔层、线路层)的对称。

4) 单板的层排布推荐方案

具体的PCB层设置时,要对以上原则进行灵活掌握,根据实际单板的需求,确定层的排布,切忌生搬硬套。以下给出常见单板的层排布推荐方案,供参考。

常见单板的层排布

| 层数 | 电源 | 地 | 信号 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 4 | 1 | 1 | 2 | S1 | G1 | P1 | S2 | ||||||||

| 6 | 1 | 2 | 3 | S1 | G1 | S2 | P1 | G2 | S3 | ||||||

| 6 | 1 | 1 | 4 | S1 | G1 | S2 | S3 | P1 | S4 | ||||||

| 8 | 1 | 3 | 4 | S1 | G1 | S2 | G2 | P1 | S3 | G3 | S4 | ||||

| 8 | 2 | 2 | 4 | S1 | G1 | S2 | P1 | G2 | S3 | P2 | S4 | ||||

| 1000 | 2 | 3 | 5 | S1 | G1 | S2 | P1 | S3 | G2 | P2 | S4 | G3 | S5 | ||

| 10 | 1 | 3 | 6 | S1 | G1 | S2 | S3 | G2 | P1 | S4 | S5 | G3 | S6 | ||

| 12 | 1 | 5 | 6 | S1 | G1 | S2 | G2 | S3 | G3 | P1 | S4 | G4 | S5 | G5 | S6 |

| 12 | 2 | 4 | 6 | S1 | G1 | S2 | G2 | S3 | P1 | G3 | S4 | P2 | S5 | G4 | S6 |

在层设置时,若有相邻布线层,可通过增大相邻布线层的间距,来降低层间串扰。对于跨分割的情况,确保关键信号必须有相对完整的参考地平面或提供必要的桥接措施。

Ø 阻抗控制

特征阻抗是入射波的电压与电流的比值,或反射波的电压与电流的比值。传输线的延迟和特征阻抗是由所用的PCB印制线的横截面几何形状和绝缘材料计算得到。

由于受PCB印制线制造时诸如最大绝缘厚度和最小印制线宽度的制约,电路板通常在40~75欧姆范围内控制特征阻抗。器件的输出电阻一般10几欧姆左右,因此始端串联匹配时电阻一般选33欧姆左右与走线的阻抗匹配。

1) 在进行阻抗计算时,需要考虑半固化片和芯板种类。PCB生产厂家的PCB采用两种介质:芯材和半固化片。芯材和半固化片的交替叠加构成PCB板。

2) 芯材是两面附有铜箔的介质,有十几种规格:0.1mm、0.2mm、0.3mm、0.4mm、0.5mm、0.6mm、0.7mm、0.8mm、0.9mm、1.0mm、1.2mm、1.5mm、1.6mm、2.0mm、2.4mm。各种规格的芯板除去铜厚后,介质的厚度如下表:

各种芯板的介质厚度

| 芯板规格(mm) | 0.1 | 0.2 | 0.3 | 0.4 | 0.5 | 0.6 | 0.7 | 0.8 |

| 介质厚度(mil) | 1.18 | 5.12 | 9.06 | 12.99 | 16.83 | 20.87 | 24.8 | 28.74 |

| 芯板规格(mm) | 0.9 | 1 | 1.2 | 1.5 | 1.6 | 2 | 2.4 | |

| 介质厚度(mil) | 36.61 | 44.49 | 52.36 | 56.3 | 60.24 | 75.98 | 91.73 |

注意:在进行阻抗控制的时候,一定要考虑到芯板的厚度中包含了铜箔的厚度。

3) 半固化片有1080、2116、7628三种,1080的厚度为3.0mil,2116的厚度为4.2mil,7628的厚度为7.0mil,可以选择任意片数,组合使用。出于生产上的原因,除芯板之外的每层介质至少选择两片以上的半固化片进行组合。由于半固化片在受热层压期间,会出现流胶的现象,使得介质的厚度变薄。因为流胶后1080的厚度变为2.5mil,7628的厚度变为6.5mil,当选用较薄的介质厚度时,应特别注意这种现象。

4) 铜箔的厚度:目前我司的PCB板中铜箔的厚度一般为:表层1.8mil,内层1.4mil。

6.5.3. 信号质量测试需求

Ø 熟悉硬件设计方案及单板上的关键信号,明确哪些信号是SI 的测试重点(信号质量测试、时序测试、IBIS模型验证)。

Ø 在PCB布线阶段就要求开发人员预留关键信号的测试孔,同时在板上各部分均匀地布上适宜数量的地孔以方便测试。

Ø 因为传输线效应的影响,探针的位置和需要测试的管脚位置越远,波形相差就越大。首先选择探头直接搭在接收器件信号的IC引脚上测试信号(不会引起短路),对于BGA及细小管脚的SMT器件引脚,则选择最靠近接收器件信号管脚的信号线上的过孔(或测试孔)进行测试,对这一类信号应该在接收芯片附近留有过孔(或测试孔)以方便测试。

Ø 对有同步时序测量要求的网络,因为时钟信号是同步时序测试的参考点,为了方便时序测试,应同时在发送和接收器件的时钟信号管脚附近放置测试孔,以便测试信号的相关时序参数。

Ø 对有阻抗测试要求的单板,在PCB设计时建议在控制阻抗的信号层的空白区布1根(单线)或2根(差分线)大于4inch的线,并用SMA插座引出以便测试使用。

6.6. DFM

6.6.1. PCB尺寸设计一般原则

Ø 可加工的PCB尺寸范围为(mm):长(51 ~ 508)X 宽(51~457)X厚(1.0~4.5)X 倒角(≥3) X 传送边禁布区(≥5),宽厚比小于等于150。

Ø 板尺寸<85mm×85mm时,推荐做拼板,当拼板需要做V-CUT时,板厚应小于3.5mm。拼板方式有三种:同方向拼板、中心对称拼板、镜象对称拼板。

1) 常用同方向拼板。平行传送边方向上拼板数量不应超过2,如果单元板尺寸很小时,在平行传送边的方向拼板数量可以超过3,但垂直于单板传送方向的总宽度不能超过150mm。当外形不规则或有器件超出板边时,可采用铣槽+V-CUT的方式。

2) 中心对称拼板主要适用于两块形状较不规则的PCB。将不规则形状的一边相对放置中间,使拼板后形状变为规则。不规则形状的PCB对拼,中间必须开铣槽才能分离两个单元板。如果拼板产生较大的变形时,可以考虑在拼板间加辅助边(用邮票孔相连)。有金手指的板需拼板时,采用金手指朝外。

3) 采用镜象对称拼板时需注意正反面都是SMD;SMD都能满足背面过回流焊要求;光绘层设置的正负片对称分布;镜象对称拼板后的辅助边的MARK基准点翻转必须重合。

Ø 加辅助边情况

如果传送边禁布区不能满足5mm时,必须在相应的板边每边增加≥5mm宽的辅助边。 若辅助边较长不易掰板时,可以分段加辅助边(每段辅助边的长度推荐100mm)。

送边一侧器件伸出PCB外时,辅助边的宽度要求最少比伸出板边的器件 ≥5mm。如果器件需要沉到PCB内,与辅助边干涉时,辅助边要开铣槽避开器件,开口的四边要比器件沉入PCB的尺寸大0.5mm。

过波峰焊且板边或板内有大于35mm×35mm大面积的空缺的板,应在空缺处应加辅助块。辅助块用邮票孔与PCB相连。

PCB板边有缺角或不规则的形状时,且不能满足PCB外形要求时,应加辅助块补齐,使其规则,方便设备组装。

对于需要及其自动分板的PCB,V-CUT线(TOP&BOTTOM面)要求保留1mm的器件禁布区,以避免在自动分板时损坏器件。

Ø 常用的PCB连接方法

1) V-CUT:板直线连接,采用V-CUT的拼板板间距应设置为5mil。

2) 邮票孔:孔径为1.0mm/40mil的非金属化孔,孔中心间距为1.27mm/50mil,邮票孔向PCB的主体板边缩进0.4mm/16mil。PCB与PCB和PCB与辅助边的连接推荐采用折断桥(Breakaway Bridge)的方式,折断桥的长度为4.00mm。

3) 铣槽:铣槽的宽度推荐≥2mm,铣槽常用于单元板之间需留有一定距离的情况,一般应与V-CUT或邮票孔配合使用。

大面积的板边和板内空缺:辅助块与PCB的连接一般采用铣槽+邮票孔的方式,辅助块的长度大于50mm时,折断桥应有2个,当长度小于50mm时,可以用1个折断桥。

6.6.2. 基准点ID的设计

Ø 基准点的分为:拼板基准点,单元基准点,局部基准点。

Ø 过SMT回流焊的单板必须放置基准点,单面基准点数量≥3 ;在板边呈“L”形分布,基准点圆心远离传送边6mm以上;单面SMT时只需器件面放置基准点; PCB双面布贴片器件时基准点双面放置。

Ø 拼板基准点和单元基准点采用标准封装库:ID-BOARD。实心圆为40mil,阻焊开窗80mil,有 2mm八边形铜线边作保护圈用。

Ø 间距≤0.4mm的QFP和间距≤0.8mm BGA、CSP、FC等器件需要放置局部基准点。局部基准点为:实心圆为40mil,阻焊开窗为50mil,外圈铜环可不要。

6.6.3. 器件布局的通用要求

Ø 有极性或方向性的THD器件在布局上方向一致,排列整齐。

Ø 推荐器件布局方向为0°,90°。

Ø 除了接口器件等特殊需要外,其他器件本体都不能超出PCB边缘,满足引脚焊盘边缘(或器件本体)距离传送边≥5mm的要求。

Ø 需安装散热器的SMD应注意散热器的安装位置,布局时要求有足够的空间,确保不与其他器件相碰。

Ø 不同属性(如有电位差,不同的电源-地属性等)的金属件(如散热器、屏蔽罩等)或金属壳体的元器件不能相碰。

Ø 器件高度与拉手条的要求满足结构要求。

6.6.4. SMD器件布局要求

Ø SMD器件布局的一般要求

细间距器件推荐布置在PCB同一面。

1) 同种贴片器件间距要求≥12mil(焊盘间),异种器件:≥(0.13×h+0.3)mm(h为周围近邻器件最大高度差)。

2) 回流工艺的SMT器件间距列表:(距离值以焊盘和器件体两者中的较大者为测量体。下表中括弧中的数据为考虑可维修性的设计下限)。

回流工艺的SMT器件间距列表

| 单位mm | 0402~0805 | 1206~ 1810 | STC3528~ 7343 | SOT、SOP | SOJ、 PLCC | QFP | BGA

|

| 0402~0805 | 0.40 | 0.55 | 0.70 | 0.65

| 0.70 | 0.45

| 5.00(3.00) |

| 1206~1810 1206~1810 | 0.45 | 0.65 | 0.50 | 0.60 | 0.45 | 5.00(3.00) | |

| STC3528~7343 | 0.50 | 0.55 | 0.60 | 0.45 | 5.00(3.00)

| ||

| SOT、SOP | 0.45 | 0.50

| 0.45 | 5.00

| |||

| SOJ、PLCC | 0.30 | 0.45 | 5.00 | ||||

| QFP | 0.30 | 5.00 | |||||

| BGA

| 8.00 |

3) 在考虑SMD器件的兼容替代时,片式器件允许重叠,贴片与插件允许重叠,SOP器件不允许重叠。

4) BGA器件周围需留有3mm禁布区,最佳为5mm禁布区。在布局空间密度的限制条件下,chip元件允许禁布区为2mm,但不优选。一般情况下BGA不允许放置背面;当背面有BGA器件时,不能放在正面BGA的8mm禁布区的投影范围内。

5) 大于0805封装的陶瓷电容,布局时尽量靠近传送边或受应力较小区域,其轴向尽量与板传送方向平行。

6) 插拔器件或板边连接器周围3mm范围内尽量不布置SMD,以防止连接器插拔时产生的应力损伤器件。

7) 器件的焊点要方便目检,防止较高器件布置在较低器件旁时影响焊点的检测,一般要求视角≤45度。

1) 我司适合过波峰焊的SMD器件

大于等于0603封装,且Stand Off值小于0.15mm的片式阻容器件和非露线圈片式电感;

Pin间距大于等于1.27mm/50mil,且StandOff值小于0.15mm的SOP器件;

PITCH≥1.27/50mil ,引脚焊盘为外露可见的SOT器件。

2) 波峰焊接的PCB设计一般原则

器件封装库需采用波峰焊盘库。

SOP器件轴向需与过波峰方向一致。

SOP器件在过波峰尾端焊盘中心后(D+3/2d)间距处增加一对宽度为d5/2的偷锡焊盘。其中D为两个焊盘中心的间距,d为焊盘宽度。

采用波峰焊盘库的片式器件对过波峰方向无特别要求。

器件底部尽量走线以抬高点胶高度,在Stand Off值不是很理想的情况下,要求有走虚拟走线。

3) 波峰焊接工艺的SMT器件距离列表

Ø 相同类型器件距离

波峰焊接工艺的同类型SMT器件间距列表

| 封装尺寸

| 焊盘间距L(mm/mil) | 器件本体间距B(mm/mil) | ||

| 最小间距 | 推荐间距 | 最小间距 | 推荐间距 | |

| 0603 | 0.76/30 | 1.27/50 | 0.76/30 | 1.27/50 |

| 0805 | 0.89/35 | 1.27/50 | 0.89/35 | 1.27/50 |

| ≥ 1206 | 1.02/40 | 1.27/50 | 1.02/40 | 1.27/50 |

| SOT封装 | 1.02/40 | 1.27/50 | 1.02/40 | 1.27/50 |

| 钽电容3216、3528 | 1.02/40 | 1.27/50 | 1.02/40 | 1.27/50 |

| 钽电容6032、7343 | 1.27/50 | 1.52/60 | 2.03/80 | 2.54/100 |

| SOIC | 1.27/50 | 1.52/60 | --- | --- |

Ø 不同类型器件距离,焊盘边缘距离≥1.0mm。

波峰焊接工艺的不同类型SMT器件间距列表

| 封装尺寸(mm/mil) | 0603~1810 | SOT | STC3216~7343 | SOP | 插件通孔 | 通孔(过孔) | 测试点 |

| 0603~1810 | 1.27/50 | 1.52/60

| 2.54/100

| 2.54/100

| 1.27/50

| 0.6/24 | 0.6/24 |

| SOT | 1.27/50

| 2.54/100

| 2.54/100 | 1.27/50 | 0.6/24 | 0.6/24 | |

| STC3216~7343 | 2.54/100 | 2.54/100 | 2.54/100

| 2.54/100

| 1.27/50

| 0.6/24 | 0.6/24 |

| SOP | 2.54/100 | 2.54/100 | 2.54/100

| 1.27/50 | 0.6/24 | 0.6/24 | |

| 插件通孔 | 1.27/50

| 1.27/50 | 1.27/50 | 1.27/50 | 0.6/24 | 0.6/24 | |

| 通孔(过孔) | 0.6/24 | 0.6/24 | 0.6/24 | 0.6/24 | 0.6/24 | 0.3/12 | 0.3/12 |

| 测试点 | 0.6/24 | 0.6/24 | 0.6/24 | 0.6/24 | 0.6/24 | 0.3/12 |

6.6.5. THD布局要求

Ø THD布局通用要求

除结构有特别要求之外,都必须放置在正面。

相邻器件本体之间的距离≥20mil。

Ø 通用波峰焊布局要求

优选引脚间距(pitch)≥2.0mm,焊盘边缘间距≥40mil的器件。 在器件本体不相互干涉的前提下,相邻器件焊盘边缘间距满足≥40mil。

THD每排引脚数较多时,以焊盘排列方向平行于进板方向布置器件。当布局上有特殊要求时,焊盘排列方向与进板方向垂直时,应在焊盘设计上采取适当措施提高工艺窗口,如椭圆焊盘的应用。当相邻焊盘边缘间距为0.6mm-1.0mm(24-40mil)时,推荐采用椭圆形焊盘或加偷锡焊盘。

Ø 选择性波峰焊的布局要求

需要单个处理的焊点的中心周边5.0mm区域内不应布置其他焊点或SMT器件。

需要焊接的单排多引脚穿孔器件引脚中心距不小于1.27mm,距离焊点中心3.0mm区域内不能布置其他焊点或SMT器件,满足焊盘边远距离≥0.6mm,对1.27mm间距器件,焊盘需要盖绿油或作无焊盘设计。

如果需要焊接的单排多引脚穿孔器件只有一侧布置有SMT器件和焊盘时,则不同的器件排布方向其加工能力不同,当器件平行于待焊点布置时,最小可加工焊盘边缘间距为2.0mm,如果器件垂直待焊点布置时,最小可加工焊盘边缘间距为1.0mm。

需要焊接的多排穿孔器件引脚中心距≥1.27mm的,距离焊点中心3.0mm区域内不能布置其他焊点或SMT器件。

6.6.6. 压接件器件布局要求

Ø 弯/公、弯/母压接器件面的周围3mm不得有高于3mm的元器件,周围1.5mm不得有任何焊接器件;在压接器件的反面距离压接器件的插针孔中心2.5mm范围内不得有任何元器件。

Ø 直/公、直/母压接器件周围1mm不得有任何元器件; 对直/公、直/母压接器件其背面需安装护套时,距离护套边缘1mm范围内不得布置任何元器件,不安装护套时距离压接孔2.5mm范围内不得布置任何元器件。

Ø 欧式连接器配合使用的接地连接器的带电插拔座,长针前端6.5mm禁布,短针2.0mm禁布。

Ø 2mmFB电源单PIN插针的长针,对应单板插座前端8mm禁布。

6.6.7. 通孔回流焊器件布局要求

Ø 布局要求

1) 对于非传送边尺寸大于300mm的PCB,较重的器件尽量不要布置在PCB的中间,以减轻由于插装器件的重量在焊接过程中对PCB变形的影响,以及插装过程对板上已经贴放的器件的影响。

2) 为方便插装,器件推荐布置在靠近插装操作侧的位置。

3) 尺寸较长的器件(如内存条插座等)长度方向推荐与传送方向一致。

4) 通孔回流焊器件焊盘边缘与pitch≤0.65mm的QFP、SOP、连接器及所有的BGA的之间的距离大于20mm。与其他SMT器件间距离>2mm。

5) 通孔回流焊器件本体间距离>10mm。

6) 通孔回流焊器件焊盘边缘与传送边的距离≥10mm;与非传送边距离≥5mm。

Ø 禁布区要求

1) 通孔回流焊器件焊盘周围要留出足够的空间进行焊膏涂布,在禁布区之内不能有器件和过孔。

2) 必须放置在禁布区内的过孔要做阻焊塞孔处理。

6.6.8. 走线设计

Ø 线宽/线距

1) PCB加工推荐使用的线宽/间距≥5mil/5mil,最小可使用的线宽/间距为4mil/4mil。

2) 走线和焊盘的距离:外层走线和焊盘的距离与内层走线距离孔环的距离要求一致。

3) 外层走线和焊盘的距离必需满足走线距离焊盘阻焊开窗边缘≥2mil。

Ø 出线方式

一般原则:所有元器件焊盘走线除特殊要求外,均要满足热设计要求。

1) CHIP器件焊盘的出线方式

CHIP器件走线和焊盘连接要避免不对称走线。

图6-6-1 CHIP器件焊盘对称出走图

2) IC器件焊盘出线方式

IC类元器件走线应从焊盘端面中心位置连接。可以按下图a)所示走线,但禁止图b) 所示。

图6-6-2 IC器件焊盘中心出线图A

图6-6-3 IC器件焊盘中心出线图B

当和焊盘连接的走线比焊盘宽时,走线不能覆盖焊盘,应从焊盘末端引线,如下图中的(a)。

密间距地SMT焊盘引脚需要连接时,应从焊脚外部连接,不允许在焊脚中间直接连接,如下图中的b)。

对于密间距的IC,走线从焊盘出线时,宽度不能比焊盘宽。如下图:

图6-6-4 IC器件焊盘中心出线图C

3) 走线和过孔的连接

为保证走线和过孔连接的可靠性,弥补钻孔偏差的影响,推荐所有走线和过孔的连接处采用下述三种方法处理:Filleting(teardrop),Corner Entry,Key Holing。

图6-6-5 过孔和走线连接

Ø 走线的安全性

1) 距离要求

走线距板边距离>20mil。内层电源/地距板边距离>20mil。

接地汇流线及接地铜箔距离板边须>20mil。

在有金属壳体(如:散热器、电源模块、金属拉手条、卧装电压调整器、晶振、铁氧体电感等)直接与PCB接触的区域不允许有走线。器件金属外壳与PCB接触区域向外延伸1.5mm区域为表层走线禁布区。

走线距非金属化孔的最近距离

| 走线距离孔边缘的距离 | ||

| NPTH<80mil | 安装孔 | 见安装孔设计 |

| 非安装孔 | 8mil | |

| 80mil<NPTH<120mil | 安装孔 | 见安装孔设计 |

| 非安装孔 | 12mil | |

| NPTH>120mil | 安装孔 | 见安装孔设计 |

| 非安装孔 | 16mil | |

2) 与插框槽相关的禁布区

PCB在机框内插拔时,为了避免损伤走线,在PCB和金属插框槽接触的区域不允许走线。

Ø 走线的热设计

一般情况下,要求SMT焊盘两端的热容量尽量相当,走线宽度一般不能大于焊盘的三分之二宽度,否则,很容易在过回流时产生器件直立现象。当有焊盘需和大面积铜箔连接时,焊盘与铜箔间应以“米”字形或“十”字形线连接,以增加与铜箔间的热阻,防止加工时焊盘热量传导过快影响焊点可靠性。有大电流通过的插件焊盘,为了保证电气连接应在焊盘旁边增加金属化过孔。

6.6.9. 孔设计

Ø 安装孔

1) 布局:孔的位置严格按照结构要素图要求布局。

| 类型 | 紧固件的直径规格(单位:mm) | 表层最小禁布区直径范围(单位:mm) | 内层最小无铜区(单位:mm)

| |

| 金属化孔孔壁与导线最小边缘距离 | 电源层、接地层铜箔与非金属化孔孔壁最小边缘距离 | |||

| 螺钉孔 | 2 | 7.1 | 0.4

| 0.63

|

| 2.5 | 7.6 | |||

| 3 | 8.6 | |||

| 4 | 10.6 | |||

| 5 | 12 | |||

| 铆钉孔 | 4 | 7.6 | ||

| 2.8 | 6 | |||

| 2.5 | 6 | |||

| 定位孔、安装孔等 | ≥2 | 安装金属件最大禁布区面积+A(注) | ||

注:A为孔与导线最小间距,参照内层最小无铜区。

Ø 定位孔

Ø 过孔

1) 过孔不能位于焊盘上;

2) 器件金属外壳与PCB接触区域向外延伸1.5mm区域内不能有过孔。

3) 贴片胶点涂或印刷区域内不能有过孔。如采用贴片胶点涂或印刷工艺的CHIP、SOP元件下方的PCB区域。

Ø 埋、盲孔设计

6.6.10. 阻焊设计

Ø 阻焊设计原则

1) PCB和金属安装导轨的配合面不应有阻焊。

2) 阻焊开窗应比焊盘尺寸大6mil以上(一边大3mil)。

3) 相邻SMD的焊盘、SMD焊盘和THD孔、SMD焊盘和过孔、过孔和过孔之间要保留阻焊桥, 最小阻焊桥宽度2~4mil,以防止焊锡从过孔流走或短路。

4) 散热用途的铺铜应作阻焊开窗。

5) 引脚间距小于0.5mm(20mil)的SMD器件,不管CAD文件上引脚间是否有阻焊桥,厂家一般都不会做阻焊桥,如果需要要在图上特别注明。

Ø 孔的阻焊设计

1) 一般过孔的阻焊开窗正反面均为孔径+5mil。

2) 测试孔的阻焊开窗正面为孔径+5mil和反面为焊盘直径+8mil。

3) 安装孔正反面禁布区内应作阻焊开窗。

4) 非金属化定位孔正反面阻焊开窗比孔径大10mil。

Ø BGA的过孔塞孔和阻焊设计

1) 需要塞孔的孔在正反面都不作阻焊开窗。

2) 见本规范的6.7章节的测试点设计要求。

Ø 走线的阻焊设计

走线一般要求覆盖绿油。射频PCB出于阻抗控制的需要有可能使走线裸露。

Ø 金手指的阻焊设计

金手指的阻焊开窗应开整窗,上面和金手指的上端平齐,下端要超出金手指下面的板边。

6.6.11. 表面处理

我司PCB 缺省的表面处理方式为热风整平HASL。

1) 热风整平HASL

工艺要求:该工艺是指在PCB最终裸露金属表面覆盖63/37的锡铅合金。热风整平锡铅合金镀层的厚度要求为12.7um至38.1um。

热风整平工艺对于控制其镀层的厚度和焊盘图形较为困难,不推荐使用于有细脚距器件的PCB,原因是细脚距器件(≤0.4mm)对焊盘平整度要求高;热风整平工艺的热冲击可能会导致PCB翘曲,厚度小于0.7mm的超薄PCB不推荐采用该表面处理方式。

2) 化镍浸金ENIG

工艺要求:化镍浸金俗称化学镍金,PCB的铜金属面采用非电解镍层厚度为2.5um~5.0um,浸金(99.9%的纯金)层的厚度为0.08um~0.23um。

适用范围:因能提供较为平整的表面,此工艺适于细脚距器件的PCB。

3) 有机可焊性保护层OSP

此工艺是指在裸露的PCB铜表面用特定的有机物进行表层覆盖,目前唯一推荐的该有机保护层为Enthone's Entek Plus Cu-106A,其厚度要求为0.2um~ 0.5um,因其能提供非常平整的PCB表面,尤其适合于密脚距PCB。

4) 沉锡Immersion Tin

5) 选择性电镀金Gold fingers

选择性电镀金表面处理是指在PCB铜表面先用涂敷镍层,后电镀金层。镍层的厚度为2.5~5.0微米,金层的厚度为0.8~1.3微米。“金手指”一般采用此表面处理方式。

6.6.12. 丝印设计

丝印设计包括:元器件丝印、板名、版本号、条码丝印、安装孔定位孔丝印、过板方向标志、扣板散热器、防静电标志、定位识别点等。

Ø 丝印设计通用要求

1) 为了确保所有字母、数字和符号在PCB上便于识别, 丝印的线宽必须大于5mil,丝印高度至少为50mil。

2) 丝印不允许与焊盘、基准点重叠。

3) 白色是默认的丝印油墨颜色,如有特殊需求,需要在PCB钻孔图文件中说明。

4) 在高密度PCB设计中,可根据需要选择丝印的内容。

5) 丝印字符串的排列方向从左至右、从下往上。

Ø 元器件丝印设计要求

1) 所有元器件、安装孔、定位孔以及定位识别点都有对应的丝印标号,且位置清楚、明确。

2) PCB上有极性或安装方向性的元器件,其极性和方向均应在丝印上体现出来。

3) 丝印与需要焊接的地方如SMT焊盘、插装焊接孔、测试点、基准点至少距离0.4mm。

4) 为了方便可检验性,丝印字符、极性与方向的丝印标志不能被元器件或拉手条等覆盖。

5) 如果PCB上由于空间的限制,只能取消某些元件的丝印符号时,必须保证在PCB的装配图上有这些元件的丝印符号。通过装配图来定位元件。

Ø 板名版本丝印

1) 板名、版本应放置在PCB的元件面上,板名、版本丝印在PCB上应水平放置。 双面布局扣板正反面都需要有板名、版本丝印。

2) 板名丝印的字体大小以方便读取为原则,一般比器件序号丝印大。

Ø 条形码丝印

1) 条形码丝印水平/垂直放置。

2) 条形码位置以不盖住焊盘、测试孔、不被拉手条盖住和便于读取信息为原则。

3) 距板边5mm,距离拉手条15mm。优选的放置顺序为:如下图所示:

|

|

图6-6-6 条形码丝印优先放置顺序图

4) 单面器件板:Top面实线框→Top面虚线框;双面器件板:均为实线框。

5) 所有新增单板必须预留条形码位置。

6) 有MAC地址需求的单板,必需增加MAC地址标签(大小42*6),并布放在PCB 的Top面。条形码框内注明:MAC ADDRESS 。

7) 条形码丝印框大小优选次序: 42*8mm→42*6mm→7*9mm。 42*8适用于过自动线的单板。

Ø 其他丝印

1) 定位识别点的位置序号统一用ID**表示。

2) 安装孔在PCB上的位置代号建议为“M**”,定位孔在PCB上的位置代号建议为“P**”。对于扣板,需要双面标示。

3) 所有射频PCB要求标注“RF”的丝印字样。

4) 有光纤盘绕的PCB,需要在PCB标示出光纤的盘绕途径。

5) 对于过波峰焊的过板方向有明确规定的PCB需要表示出过板方向。 适用情况:PCB上设计了偷锡焊盘、泪滴焊盘、或器件波峰焊接方向有特定要求等。

6) 如果有扣板、散热器,要用丝印将扣板、散热器的轮廓按真实大小标示出来,若丝印与器件干涉时,应用间隔的丝印将扣板外形进行标识。

7) 当PCB上的芯片功耗较大,需要安装散热器。若板上空间允许,需要在PCB上用丝印将散热器的轮廓按真实大小标示出来。若丝印与周边器件干涉时,应用间隔的丝印将散热器外形进行标识。

8) 安规的防静电标记丝印采用标准库,优先放置在PCB的元件面。

6.6.13. 尺寸和公差标注

Ø 尺寸标注的标准化要求

1) PCB的尺寸和公差要求标注在钻孔图文件(Drill chart)中。

2) 有公差要求的孔径的大小尺寸、公差、镀涂厚度要求在钻孔图中注明。

3) PCB板尺寸标注基准和结构要素图相同。

4) 尺寸的单位采用mil。

5) PCB加工通用尺寸公差表。

6) PCB的公差要求(板厚、外形尺寸、孔径)超过通用要求时,应该在钻孔图文件中注明。

Ø 需要标注的尺寸及其公差

1) PCB的外形尺寸,四角的倒角尺寸。

2) 定位孔、安装孔(螺钉安装孔、铆接孔)的位置尺寸和公差。

3) 板厚的尺寸和公差。

4) 开窗的位置和大小尺寸。

5) 特殊孔的孔径大小尺寸、特殊公差和特殊镀涂要求。

6) 插板连接器、扣扳连接器的位置尺寸和公差。

7) 导销、导套的安装位置尺寸和公差。

8) 和拉手条等结构件有装配关系的网口连接器、光纤连接器、指示灯等的位置尺寸和公差。

6.6.14. 背板部分

Ø 背板尺寸设计

1) 背板六种主流工艺:

单面/双面SMT + 压接连接器 + 压装护套 + 螺钉/螺母安装器件的装配

波峰焊/手工焊接 + 压接连接器 + 铆接护套 + 螺钉/螺母安装器件的装配

波峰焊/手工焊接 + 压接连接器 + 螺钉/螺母安装器件的装配

压接连接器 + 压装护套 + 螺钉/螺母安装器件的装配

压接连接器 + 螺钉/螺母安装器件的装配

压接连接器

2) 拼板方式

厚度≥3 mm或外形尺寸大于80*100mm的背板一般不允许拼板;没有焊接工艺的背板不允许拼板。

3) 开窗和倒角处理

背板四角的倒角R≥5mm;背板开窗四角倒角R≥2mm。外形非方形且需要SMT的背板,其外形要求参见单板部分。

Ø 背板布局

1) 基本要求

背板原则上不允许布置有源器件;不允许在一块背板上同时采用THT、SMT焊接工艺。

结构要素图上有位置要求的连接器和插座应严格按照结构要素图放置。

2) SMD、THT、阻容器件

SMC器件在空间允许的情况下要求布置在同一面;

两面都必须布置SMC时,将重量重、体积大的布置在同一面;

有极性的 SMC在板上方向尽量一致;同类型的器件排列整齐美观。

THD焊接器件布置在背板的同一面,一般要求布置在背板的B面。

1) 背板和插框、加强筋接触区域向外延伸1mm禁布器件、走线、金属化过孔。

2) 欧式连接器禁布区

欧式连接器周围3mm禁布器件;

欧式连接器的背面距离压接孔中心周围2.5mm,距离护套2mm禁布器件。

需采用波峰焊接的母板,尽量不要把焊接器件布置在欧式连接器的两头及中间槽位区域。

3) 2mm、HS3连接器禁布区

SMD阻容器件:不允许布置在连接器周围0.5mm范围内和距离背面压接孔中心2.5mm,护套1.0mm范围内。

THT阻容器件:不允许布置在连接器周围3mm范围内,背面距离压接孔3.5mm,距离护套2.5mm范围内。

连接器、拨码开关:不允许布置在连接器周围10mm范围内,背面距离插针孔10mm或护套9mm范围内。

Ø 丝印设计

1) 背板的前后面都必须有板名、版本号、前(F)后(B)标识,优先考虑放在板的右上角,且不能被覆盖或放置在绿油开窗区。布局困难的,允许上下平行移动来布置。前后面标识应置于前后面的板名、版本后面或下面,并与其保持2~3mm的间隔。 以“F”表示PCB板的前面(front),以“B”表示PCB板的后面(back)。 板名、版本丝印方向和背板的长度方向平行,字体高度大于2.5mm。

2) 元器件

元器件标识丝印位置和相应器件对应,从属唯一,不易混淆;方向和器件长度方向垂直或平行。

3) 槽位标识

槽位标识字符一般应与所插入单板的名称对应,兼容设计的背板槽位标识可采用数字,并在数字外加圆,如①、②。

槽位标识一般应置于PCB相应槽位连接器的正下方3~5mm处;前面插板后面出线的的背板,槽位标识一般放在背板的后面;前面插板后面封闭的背板,槽位标识一般放在背板的前面;前后双面插板的背板,前后面都需要标注槽位标识。槽位标识字高大于2.5mm。

槽位标识可在插框上相应的位置标注。

4) 关键信号和开关状态

关键信号点,电源连接器引脚的电压数值、地属性,拨码开关的状态,标注在相应的引脚处,丝印字符高大于2.5mm。

5) 条形码丝印

条码框一般布置在背板的B面,背面封闭的插框条码布置在背板的F面。

6.7. DFT设计要求

在PCB设计所涉及的DFT设计中,主要有ICT测试点和功能信号测试点两个方面。

6.7.1. PCB的ICT设计要求

Ø ICT设计规定

1) 装备组组长对测试策略中“单板是否要求ICT”的决定 ,必须明示到原理图项目人和CAD设计人。

2) ICT工程师在PCB布局评审时,最终确定是否必须要ICT设计。不需要的,必须与装备组组长确定出其他测试方案,并反映在工艺文件中。

3) 对有ICT设计的单板,CAD室需考虑相关工作量,拟定相应的设计计划。

4) 在布线评审时,CAD设计人员应完成ICT可测性设计,ICT应评审通过。

5) 对第4条不满足的情况下,CAD与ICT协调,可以在布线评审后完成ICT可测性设计,但ICT在布线评审意见栏中应明示“ICT设计不满足要求”等字样。CAD人员应注意在投板前确认ICT审查通过。

6) 在可测性设计过程中,ICT工程师应积极配合CAD人员,在不影响测试覆盖的情况下,尽量减少测试点,给CAD设计更大的灵活性。对高复杂度单板给出可省略的测试点网络。

7) CAD设计人在投板前,应确认ICT审查已经OK或基本OK。在工艺审查节点,工艺人员必须征求ICT意见,ICT是否通过;对不能肯定没有ICT的,当有ICT处理。在流程评审中,ICT审查主要是最后确认,不能对PCB再有大的修改和要求。

8) CAD设计人在启动两个电子流前,没有经过ICT的确认,而导致流程返回,影响计划的进度的由CAD设计人负责。

9) 对个别单板,若项目人明确表示下一版本有较大改动的(需有记录证明),ICT可不进行测试完备性审查。

1) 2或3个非金属化(D=125-0+3 mil)定位孔,应放置于单板的三端,为非对称方式。

2) 同一类型的板(如交换、SDH)的定位孔的位置和大小应该相同。

3) 定位孔在板的Bottom面中心125mil范围不能有器件及测试点;不能被安装在板上的器件(如连接器、拉手条)挡住。

1) 测试点的焊盘为32mil或40mil。优选用焊盘为40mil的测试点库:TVIA10-40、TVIA12-40 、TVIA16-40、 ICT-SMD40。 可选用标准库中的TVIA10-32、TVIA12-32 、TVIA16-32、 ICT-SMD32。如果增加其他的Via及盲孔做测试点,其焊盘直径也必须为32mil或40mil。

2) 通孔器件的器件脚(Drill hole)也可做测试点,但以下类型不能当作测试点:

器件脚露出PCB板面超过2mm;

厚膜器件管脚;

采用通孔回流焊或人工补焊器件的管脚;

经过加工及不规则的器件管脚;

3) 测试点或定位孔不能被其他固定在单板上的固件如散热片、加固件、拉手条、接插件、压接件、条形码、标签等的外形轮廓挡住。

4) 背面丝印不可盖住测试点焊盘。

5) 测试点间距要求

两个测试点中心间隔d:最好85mil;接受70mil;尽量避免50mil。

测试点到过孔的间距d:最好20mil;最小12mil。

测试点到底面器件焊盘边间距d: 最好20mil;最小12mil。 对于过波峰焊的单板,最好40mil;最小25mil。

测试点到焊锡面走线的间距d:最好为20mil;最小为12mil。

测试点到PCB板边的间距d:最小125mil。 只有做密封圈夹具才有此要求。

测试点到定位孔的间距d:最好200mil;最小125mil。 便于定位柱安装。

6) 测试点密度

SMT区的针密度一般不要超过34针/每平方英寸(每平方厘米5~6个点),测试针平均分布,不要集中在某一区域。

7) 电源和地的测试点(指总电源输入点)

电源的测试点至少4个以上,而且与其它测试点间距>85mil,避免<70mil。超过2A电流的,每增加1A,应多提供一个测试点。测试点应提供在连接器及保险的前端。典型的探针每针可承受最大2A电流,间距的要求是为了能使用100mil的测试针,并避免电源与其它网络短路。

额外的地线点(指工作的数字地):每板上最少4个地线点。每5个IC应多设计一个地线点,地线点要求均匀分布在单板上。有利于减少测试干扰。

单板若有波峰焊流程或BGA的Pitch为1.0mm(不含)以下:BGA过孔都采用绿油塞孔方法,过孔两面的焊盘均被绿油覆盖,BGA下的ICT测试焊盘采用狗骨头形状从过孔引出,以下为示意图,其中较小的为过孔,较大的为ICT测试盘。便于厂家塞孔,建议过孔孔径应小于或等于12mil。如果由于板厚原因,导致孔径超出12mil,请和厂家协商确认。ICT测试盘选用请参照封装库:ICT-SMD32 ICT-SMD40。打孔图中的文字描述为:All vias under BGA should be filled with green oil。即选用标准库BGA-WAVE。

单板没有波峰焊流程且BGA的Pitch在1.0mm以上(含):BGA下过孔既可采用上述设计方法,也可采用以下方法:测试孔不堵孔,T面按比孔径大5mil阻焊开窗,B面测试孔焊盘为32mil,阻焊开窗40mil;非测试孔需塞孔,T面、B面阻焊不开窗。测试孔优选较小的孔径;非测试孔过孔孔径应小于或等于12mil,如果由于板厚原因,导致孔径超出12mil,请和厂家协商确认。打孔图中的文字描述为:ALL vias under BGA should be filled withgreen-oil except test via,which is fabricated according to the PCB film.即选用标准库BGA-Reflow。

|

|

BGA下面的测试点推荐使用隔一个过孔布一个测试点的方法。如下图所示,蓝圈为测试点位置。可以避免测试点过密,保证间距。特别是PCB的板厚度较小的情况,避免密集的测试针局部对BGA部分施加力量。

图6-7-1 BGA下过孔加测试点图

9) ICT信号完整性考虑

对1.25G以下数字信号,可根据测试需求增加一个测试过孔。

对2.5G以上信号一般不允许加额外的测试过孔。

过孔最好在线上,不要单独引出,需引出时,引出线应尽可能短。

对差分信号,设计过孔做测试点时,必须对称使用。设计遵从CAD/SI分析结论。

Ø ICT更改原则

1) 所有工程更改影响到PCB的应当通知ICT开发工程师。ECO修改时,禁止移动测试点,这样可利用原夹具,ECO修改时多征求ICT开发工程师意见使影响最小。

2) 避免删除原测试点和移动通孔器件。 如果必须移动测试点,应将测试点移到通孔类(drill)器件的管脚(因ICT夹具在这些地方一般有预留测试孔Dummy testpoint)或其他指定点。避免做新夹具,编新程序。

3) 所有定位孔不要移动。

6.7.2. 功能和信号测试点的添加

1) 由项目人员根据功能测试的需要(主要用于单板调试及信号测试)确定要添加的功能测试点,并包含在原理图中。

2) 功能测试点的焊盘应完全开阻焊窗,以保证能进行焊接或与测试仪器探头有良好的接触。常用的功能测试点封装有:GND12、GND24等。

3) 功能测试点放置的位置应能被方便地测试到。

4) 地网络可适当均匀地在单板上放置多个,以方面测试。

5) 可根据项目人员的需要添加功能测试点的标注丝印,并保证丝印不被其他器件或结构件所遮挡。

6) 需要焊测试针的焊盘,其孔径应当满足要求。

7) 高速信号网络的测试点应尽可能靠近传输线的末端(接受端)。

6.8. 热设计要求

1) 在布置元器件时,应将除温度检测器件以外的温度敏感器件放在靠近进风口的位置,而且位于功率大、发热量大的元器件的风道上游,尽量远离发热量大的元器件,以避免辐射的影响,如果无法远离,也可以用热屏蔽板(抛光的金属薄板,黑度越小越好)隔开。

2) 将本身发热而又耐热的器件放在靠近出风口的位置或顶部,但如果不能承受较高温度,也要放在进风口附近,注意尽量与其他发热器件和热敏器件在空气上升方向上错开位置。

3) 大功率的元器件尽量分散布局,避免热源集中; 不同大小尺寸的元器件尽量均匀排列,使风阻均布,风量分布均匀。

4) 通风口尽量对准散热要求高的器件。

5) 高器件放置在低矮器件后面,并且长方向沿风阻最小的方向排布,防止风道受阻。

6) 散热器配置应便于机柜内换热空气的流通。靠自然对流换热时,散热肋片长度方向取垂直于地面方向。靠强迫空气散热时,应取与气流方向相同的方向。

7) 在空气流通方向上,不宜纵向近距离排列多个散热器,由于上游的散热器将气流分开,下游的散热器表面风速将很低。应交错排列,或将散热翅片间隔错位。

8) 散热器与同一块电路板上的其它元器件应有适宜的距离,通过热辐射计算,以不使其有不适宜的增温为宜。

9) 利用PCB散热。如将热量通过大面积铺铜(可考虑开阻焊窗)散发,或用地连接过孔导到PCB板的平面层中,利用整块PCB板来散热。

6.9. 安规设计要求

6.9.1. 线宽与所承受的电流关系

以下为MIL-STD-275关于PCB的走线线宽与承受电流的参考数据,对于瞬时电流,参照下表即可(线宽单位为英寸);对于正常工作电流,我们至少要有50%——100%的裕量, 一般情况下降额可以按1.5A/mm考虑,不会出现过流情况(不分内外层和铜箔厚度)。 对于极少量的大电流布线(如UPS、电源板),可通过表层布线,加大COPPER的厚度,以及表层布线开阻焊窗(波峰焊时着焊锡,加大COPPER的厚度)等解决。 也可使用软件计算得到的值。

电源印制导线在层间转接的过孔数应符合通过电流的要求1A/Ф0.3孔。

6.9.2. -48V电源输入口规范

1) -48V电源到除PGND外其他电路爬电距离和电气间隙大于2.0mm;

2) PGND到其他电路的爬电距离和电气间隙大于2.0mm;

3) 保险丝应在输入端最近的地方使用,不能远离输入端;

4) 保险丝要求在PCB上标明电流和电压,并要求标出更换警告;

5) EMI用的电容器件连接到PGND的,要求能够承受1000V的抗电强度测试;

6) DC/DC模块的输入输出铜箔应满足电流要求,避免铜箔过流;

7) 对于非表贴的DC/DC模块建议输入/输出铜箔不要与DC/DC在同一面,以防止无台阶的DC/DC与输入输出电气间隙不够,甚至有的会依靠阻焊剂绝缘的情况出现;

8) 对于直列安装元器件要求在最不利的方向倒下后的爬电距离满足要求;

9) -48V输入要求具有防止反插功能。

注意:各插座焊接点与铜箔的有效连接线宽,花焊盘的有效连接线宽,是否符合电流对印制线要求,是否会出现过流。

6.9.3. 有隔离变压器的接口(E1/T1口和类似端口)的安规要求

1) 保护器件接地要求

对于E1/T1网络侧的保护器件的保护接地端要求接到PGND上。

对于工作电路侧的保护器件接地端要求接到工作地上。

2) 爬电距离要求

两侧电路的爬电距离大于2.0mm。 该爬电距离以隔离变压器的原副边为分界线隔离。

PGND到工作侧电路的爬电距离大于2.0mmm。

3) E1/T1口的工作侧和网络侧最好分开布线,不要交叉,若有集中的接插件要求网络侧电路集中布防,以便于分开隔离;

4) 接口用的插座应避免与输入输出印制线共面,以免金属插座将印制线压在下面,导致电气间隙不够,甚至依靠阻焊剂绝缘。

5) 抗电强度要求:

PGND到工作电路有AC1.0Kv的抗电强度要求。

与PGND连接的电容均为高压电容或安规电容。

若该设备的接地不可靠,则爬电距离和抗电强度按网口用户端要求。

6.9.4. 网口安规要求(类似有隔离变压器的接口)

1) 保护器件接地要求

对于网络侧的保护器件的保护接地端要求接到PGND上。

对于工作电路侧的保护器件接地端要求接到工作地上。

2) 爬电距离要求

两侧电路的爬电距离大于2.0mm。 该爬电距离以隔离变压器的原副边为分界线隔离。

PGND到工作侧电路的爬电距离大于2.0mmm。

3) 抗电强度要求

PGND到工作电路有AC1.0Kv的抗电强度要求。

与PGND连接的电容均为高压电容或安规电容。

若该设备的接地不可靠,则爬电距离和抗电强度按网口用户端要求。

7.1. 布线的基本要求

7.1.1. 布线次序考虑

1) 规则驱动布线遵循的基本步骤

定义禁布区,或控制区;

若有规则约束,要求设置规则;

试布线,评估单板是否可以布通,若不能布通,需要采用策略;

Fanout后对覆盖率检查,通常要求满足100%的覆盖率;自动Fanout不能完全覆盖时,要求手工调整达到100%覆盖,采用Fanout策略;

分析单板自动布线的可行性,对初始阶段和收敛阶段进行判断;

优先布关键信号线或附有规则的信号线,规则检查,要求有规则的关键信号线满足相应的约束规则;

其次对非关键信号线走线,总体规则检查,要求非关键信号线满足普通的设计要求;

综合使用布线策略,解决冲突;

对布线进行后处理,以改善信号质量,利于加工。

2) 规则优先:若有规则存在,则优先布置有规则要求的信号线,然后布置非关键信号线;

3) 关键信号线优先:电源、摸拟信号、高速信号、时钟信号、差分信号和同步信号等关键信号优先布线;

4) 密度优先:从单板上连接关系最复杂的器件着手布线,从单板上连线最密集的区域开始布线。

7.1.2. 约束规则设置基本要求

1) 在布线之前需进行物理规则和电气规则的定义,以便在设计过程中对设计规则进行检查,使设计满足规则要求;

2) 物理约束规则应综合考虑DFM、DFT、DFA,同时也要考虑印制线的电流、电压以及禁布区和属性问题;

3) 电气约束规则应从器件资料和预仿真分析过程中合理提取。

7.1.3. 布线处理的基本要求

1) 规则驱动布线时,保证规则的合理性,使用并提供过程Do文件;

2) 过孔、线宽、安全间距避免采用极限值。

3) 规则驱动布线的过程中尽可能考虑ICT测试点设计;

4) 管脚引线尽可能从PIN中心引出;

5) 信号线与PIN间尽可能拉开距离;

6) 无通孔或机械盲孔上焊盘;

7) 走线到板边的距离通常情况下需≥2mm,在不能满足条件的情况下,至少保证不小于20mil;

8) 表面除短的互连线和Fanout的短线外,信号线尽可能布在内层;

9) 金属外壳器件下,不允许有过孔、表层走线;

10) 尽量为时钟信号、高频信号、敏感信号等关键信号提供专门的布线层,并保证其最小的回路面积。采用屏蔽和加大安全间距等方法,保证信号质量;

11) 电源层和地层之间的EMC环境较差,应避免布置对干扰敏感的信号线;

12) 有阻抗控制要求的网络应布置在阻抗控制层上;

13) 布线尽可能靠近一个平面,并避免跨分割。若必须跨分割或者无法靠近电源地平面,这些情况仅允许在低速信号线中存在;

14) 高速信号线区域相应的电源平面或地平面尽可能保持完整;

15) 平面层和布线层分布对称,介质厚度分布对称,过孔跨层保持对称;

16) 平面层分割避免出现直角或锐角;

17) 大面积敷铜时参考网络采用地网络;

18) 敷铜时避免出现直角或锐角,并且上下铜皮须有过孔相连,尤其在铜皮的边缘处,边缘相邻过孔相距约200~400mils;

19) 布线保持均匀,大面积无布线的区域需要敷铜,但要求不影响阻抗控制;

20) 布线无DRC错误,无同名网络错误;

21) 所有信号线必须倒角,倒角角度为45度,特殊情况除外;

22) PCB设计完成后无未布完的网络,且PCB网表与原理图网表一致。

7.1.4. 布线所遵循的基本规则

1) 地线回路规则

图7-1-1 地线回路规则图

环路最小规则,即信号线与其回路构成的环面积要尽可能小,环面积越小,对外的辐射越少,接收外界的干扰也越小。针对这一规则,在地平面分割时,要考虑到地平面与重要信号走线的分布,防止由于地平面开槽等带来的问题;在双层板设计中,在为电源留下足够空间的情况下,应该将留下的部分用参考地填充,且增加一些必要的地过空孔,将双面地信号有效连接起来,对一些关键信号尽量采用地线隔离,对一些频率较高的设计,需特别考虑其地平面信号回路问题,建议采用多层板为宜。

2) 串扰控制规则

串扰(CrossTalk)是指PCB上不同网络之间因较长的平行布线引起的相互干扰,主要是由于平行线间的分布电容和分布电感的作用。克服串扰的主要措施是:

加大平行布线的间距,遵循3W规则;

在平行线间插入接地的隔离线;

减小布线层与地平面的距离。

3) 屏蔽保护规则

图7-1-2 屏蔽保护规则图

对应地线回路规则,实际上也是为了尽量减小信号的回路面积,多见于一些比较重要的信号,如时钟信号,同步信号;对一些特别重要,频率特别高的信号,应该考虑采用铜轴电缆屏蔽结构设计,即将所布的线上下左右用地线隔离,而且还要考虑好如何有效的让屏蔽地与实际地平面有效结合。

4) 走线的方向控制规则

图7-1-3 走线的方向控制规则

走线的方向控制规则,即相邻层的走线方向成正交结构。避免将不同的信号线在相邻层走成同一方向,以减少不必要的层间窜扰;当由于板结构限制(如某些背板)难以避免出现该情况,特别是信号速率较高时,应考虑用地平面隔离各布线层,用地信号线隔离各信号线。

5) 走线的开环检查规则

图7-1-4 走线的开环检查规则

一般不允许出现一端浮空的布线(Dangling Line),主要是为了避免产生"天线效应",减少不必要的干扰辐射和接受,否则可能带来不可预知的结果。

6) 走线闭环检查规则

图7-1-5 走线闭环检查规则

防止信号线在不同层间形成自环。在多层板设计中容易发生此类问题,自环将引起辐射干扰。

7) 倒角规则

图7-1-6 倒角规则

PCB设计中应避免产生锐角和直角,产生不必要的辐射,同时工艺性能也不好。

8) 器件去藕规则

图7-1-7 器件去藕规则

在印制版上增加必要的去藕电容,滤除电源上的干扰信号,使电源信号稳定。推荐电源经过滤波电容后连到电源管脚上。

9) 器件布局分区/分层规则

图7-1-8 器件布局分区/分层规则

主要是为了防止不同工作频率的模块之间的互相干扰,同时尽量缩短高频部分的布线长度。通常将高频的部分布设在接口部分以减少布线长度,当然,这样的布局仍然要考虑到低频信号可能受到的干扰。同时还要考虑到高/低频部分地平面的分割问题,通常采用将二者的地分割,再在接口处单点相接。对混合电路,也有将模拟与数字电路分别布置在印制板的两面,分别使用不同的层布线,中间用地层隔离的方式。

10) 孤立铜区控制规则

图7-1-9 孤立铜区控制规则

孤立铜区的出现,将带来一些不可预知的问题,因此将孤立铜区与别的信号相接,有助于改善信号质量,通常是将孤立铜区接地或删除。在实际的制作中,PCB厂家将一些板的空置部分增加了一些铜箔,这主要是为了方便印制板加工,同时对防止印制板翘曲也有一定的作用。

11) 电源地平面完整性规则

图7-1-10 电源地平面完整性规则

对于导通孔密集的区域,要注意避免孔在电源和地层的挖空区域相互连接,形成对平面层的分割,从而破坏平面层的完整性,并进而导致信号线在地层的回路面积增大。为避免破坏平面层,做Fanout时过孔间距至少保证能走一根信号线。

12) 电源地平面层重叠规则

图7-1-11 电源地平面层重叠规则

不同电源层在空间上要避免重叠。主要是为了减少不同电源之间的干扰,特别是一些电压相差很大的电源之间,电源平面的重叠问题一定要设法避免,难以避免时可考虑中间隔地层。

13) 3W规则

图7-1-12 3W规则

为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持70%的电场不互相干扰,称为3W规则。如要达到98%的电场不互相干扰,可使用10W的间距。

14) 20H规则

图7-1-13 20H规则

由于电源层与地层之间的电场是变化的,在板的边缘会向外辐射电磁干扰。称为边沿效应。解决的办法是将电源层内缩,使得电场只在接地层的范围内传导。以一个H(电源和地之间的介质厚度)为单位,若内缩20H则可以将70%的电场限制在接地层边沿内;内缩100H则可以将98%的电场限制在内。

7.2. 布线约束规则设置

7.2.1. 物理规则设置

Ø 孔设置

1) 通孔设置

制成板的最小孔径定义取决于板厚度,板厚孔径比应小于10,常用厚径比为8,过孔优选孔径大的过孔。孔径优选系列及厚径比优选值如下表:

孔径优选系列表

| 过孔名称 | 钻孔(mils) | 器件面焊盘(mils) | 内层(mils) | 焊接面焊盘(mils) | 器件面阻焊(mils) | 焊接面阻焊(mils) |

| via40 | 40 | 60 | 80 | 60 | 45 | 45 |

| via24 | 24 | 40 | 55 | 40 | 29 | 29 |

| via20 | 20 | 35 | 50 | 35 | 25 | 25 |

| via16 | 16 | 30 | 45 | 30 | 21 | 21 |

| via12-bga | 12 | 25 | 40 | 25 | 0 | 0 |

| via12-gen | 12 | 25 | 40 | 25 | 17 | 17 |

| via10-bga | 10 | 22 | 32 | 22 | 0 | 0 |

| via10-gen | 10 | 22 | 32 | 22 | 15 | 15 |

| via8-bga | 8 | 20 | 30 | 20 | 0 | 0 |

| via8-gen | 8 | 20 | 30 | 20 | 13 | 13 |

板厚与孔径关系优选表

| 导通孔跨越的板厚度 | 3.0mm | 2.5mm | 2.0mm | 1.6mm | 1.0mm |

| 厚径比为8时最小孔径 | 16mils | 12mils | 10mils | 8mils | 8mils |

| 厚径比为10时最小孔孔径 | 12mils | 10mils | 8mils | 8mils | 8mils |

2) 机械盲孔和埋孔

机械盲孔和埋孔这两类过孔都为机械钻孔,尺寸设置参考通孔。

机械埋盲孔设计时,导通孔分布尽量对称,交叉时保证可加工性,参见下图。

图7-2-1 机械埋盲孔可加工性图

3) BGA区域导通孔选型

单板设计优选通孔。如果板厚太厚,BGA区域选用通孔不能满足设计要求时,考虑采用HDI技术设计或机械埋盲孔设计。

Ø 间距规则设置

1) 大电流网络的线宽设置必须满足本规范中6.9.1的线宽与所承受的电流关系,并按铜箔宽度的载流量参考表中的数值降额50%去选择。

2) 大电压网络的间距设置必须满足本规范中6.9.2的-48V电源输入口规定。

3) PCB加工推荐使用线宽/线间距为:6mil/6mil;可使用的最小线宽/间距为:4mil/5mil;极限最小线宽/间距:4mil/4mil。

4) BGA的管脚间隔大小直接影响到单板的布线通道数,通道数是指两Pin或两过孔间允许走线的数量。

BGA过孔间布线通道参考表

| BGA类型 | 高密通道 | 中密布线通道 | 低密布线通道 |

| 0.8mm BGA | 1 | * | * |

| 1.0mmBGA | 1 | 1 | 1 |

| 1.27mmBGA | 3 | 2 | 1 |

表中高密通道布线在设计中避免采用,以降低加工难度,提高单板的加工可靠性和直通率。

5) 绿油桥必须不小于2mil(表贴管脚密集芯片如QFP类封装除外),否则容易在加工时导致焊盘间连锡。孔规则的推荐设置如下:

ICT测试孔Test via(焊盘为32MIL)与 pin、test pin、test via、thru pin的间距设置,不得小于如下设置,并且还必须需要满足本规范.6.7.1中的测试点设计要求。

测试孔推荐间距设置

| Test Via to Through Pin | 12MIL |

| Test Via to SMD Pin | 12MIL |

| Test Via to Test Pin | 38MIL |

| Test Via to Through Via | 10MIL |

| Test Via to Test Via | 38MIL |

| Test Via to Line | 8 MIL |

| Test Via to Shape | 15MIL |

Thru pin到Thru pin、SMD Pin、Test pin的间距设置不得小于如下设置,并且还必须满足本规范中的SMD器件布局要求、THD布局要求和压接件器件布局要求。

通孔管脚推荐设置间距

| Through Pin to Through Pin | 12 MIL |

| Through Pin to SMD Pin | 12 MIL |

| Through Pin to Test Pin | 12 MIL |

| Through Pin to Through Via | 8 MIL |

| Through Pin to Test Via | 12 MIL |

| Through Pin to Line | 8 MIL |

| Through Pin to Shape | 15 MIL |

Ø 特殊布线区间的设定

1) 特殊布线区间是指单板上某些特殊区域需要用到不同于一般设置的布线参数,如某些高密度器件需要用到较细的线宽、较小的间距和较小的过孔等,或某些网络的布线参数的调整等,要求设置规则或属性进行约束(如:BGA)。

2) 禁止布线的区域在布线之前设置禁布区,禁布区满足本规范中安装孔的禁布区要求的和压接件的禁布区设计要求。

7.2.2. 通用属性设置

1) 对连接器,安装孔、定位器件均设置FIXED属性;

2) 对模块要求定义ROOM属性。

3) 进行仿真的单板,要求定义VOLTAGE、VOLTAGE_LAYER、ROUTE_TO_SHAPE属性。

7.2.3. 电气规则设置

1) BUS线要求定义拓扑结构,满足一定的Stub长度;

2) 有时序要求的信号线要定义好时序约束规则;

3) 有时延或相对时延要求的信号线要求设置延迟规则;

4) 有串扰控制要求的信号线,需要设置有串扰约束规则;

5) 有差分要求的信号,需要设置有差分约束规则

6) 对有阻抗要求的高速信号线,设置阻抗控制规则;

7) 所有规则要求都已经过仿真验证或满足明确要求(如阻抗理论值)。

7.3. 交互式规则驱动布线策略

7.3.1. 交互布线策略

1) Fanout的交互

智能Fanout与手工调整相结合;

电源地分割对Fanout的影响及调整;

相似模块Fanout Copy。

2) 布线的交互

关键信号线规则驱动布线——物理与电气规则检查并适当手工调整;

非关键信号线布线——物理规则的检查并调整。

7.3.2. 自动布线前期处理

Ø 文件保护性操作

设置有关autosave项,以适当保存有用信息。

Ø Fanout设计要求与设置

1) Fanout对布局要求

SMT器件放置时采用中心为参考点,并要求Fanout的格点与布局的格点相同;

成排且相距较近的电阻、电容,布局时建议正反错开放置(单面布局例外);

器件之间保证足够的空间来Fanout。

2) 格点设置要求

Fanout按格点进行(通常采用50mils的格点),保证两个过孔间能走两根线或一根线;

3) 对测试点的考虑

尽可能利用Fanout来设计测试点;

测试点采用对角格点上的过孔或相邻网络不同器件上的Fanout过孔,以满足测试点中心距至少不小于70mils。

Ø Fanout策略

1) Fanout基本策略

预布短连线时直接从表面走线;

检查Fanout覆盖情况;

人为地干涉Fanout,确保足够的Fanout覆盖率;

Fanout时要求按照一定的次序。从器件顺序考虑:BGA优先,并保护;从网络顺序考虑:电源地网络先于普通网络。

先Fanout一个模块或一个器件,手工调整直到满意以后将其Copy到相似的模块或器件上。

2) 不同封装的Fanout

BGA的Fanout:BGA Fanout时要注意留出四个通道;BGA Fanout完成后一般需要进行protected;管脚的Fanout线宽设置约为PIN直径的2/3,电源地和信号线统一Fanout线宽;

小器件的Fanout :小器件Fanout时方向朝外扇出,通常小器件布局采用50mils格点;

金手指、SOP、QFP的Fanout:手工Fanout一个管脚,然后拷贝其Fanout至其它相似的管脚上。

3) Fanout覆盖率低的处理方法

电源地平面分割不合理时,适当分割电源地平面或调整布局;

禁布区不小心被加在了器件的管脚上时,考虑调整布局或Keepout区域;

一些pin间距比较小的器件的电源、地管脚的布线宽度设置不正确,需要适当调整走线宽度或调整布局;

Fanout的空间不够,需要对布局做适当调整或采用小的过孔、窄的线宽,以便有足够的空间来Fanout。

7.3.3. 不同类型单板布线策略

Ø 类型一PCB布线策略

1) 类型一主要特征如下:严格的长度规则、严格的串扰规则、拓扑规则、差分规则、电源地规则等。

2) 关键网络的处理:总线

定义Class;

要求满足一定的拓扑结构、stub及其长度(时域)约束条件;

图7-3-1 平衡菊花链和中间驱动菊花链图

设置虚拟管脚来控制拓扑结构;

图7-3-2 虚拟T点图

对STUB进行限制。设置最大的stub长度,延迟/长度应给定范围;禁止从焊盘的长边出线;允许终端带有交叉点(junction)。

3) 关键网络的处理:时钟线

定义Class,设置足够的线间距或Class与Class之间的间距;

将时钟线设置在特定的层和区域内。

4) 关键网络的处理:差分线

一般需指定布线层;

采用parallel方式,避免用tandem方式;

定义两差分线的长度匹配以及差分对长度匹配;

设置差分线对之间的间距通常的做法是将差分对定义为class,然后定义Class toclass的间距。

5) 串扰控制

网络组之间要有足够的Clearance;如:数据线、地址线和控制线之间要有间距约束,把这些网络设置成相应的class,然后在数据线和地址线之间、数据线和控制线之间、地址线和控制线之间设置串扰控制规则。

6) 屏蔽

屏蔽方式:并行(parallel)、同轴(coaxial)、级联(tandem);

规则设置好以后,可以采用手工或自动布线。

Ø 类型二PCB布线策略

1) 类型二PCB设计既具有物理实现的挑战也具有电气规则实现的挑战。

2) 在布线过程中需要进行“引导”,如:Fanout、层分割、自动布线过程控制、禁布区定义、布线次序等需要适当地进行干涉。

3) 测试并分析布线的可行性;

4) 首先考虑物理规则的实现,其次才是电气规则的实现;

5) 对产生的冲突或错误,要求综合分析其原因,有针对性地调整布线策略。

7.3.4. 规则驱动布线后期处理

Ø 测试点处理

1) 若在规则驱动的布线过程中若未对测试点进行处理,需要在后期按ICT要求设置规则进行处理。具体要求参看本规范中的DFT设计要求。

Ø Spread Wires

Ø 倒角

1) 在倒角之前最好能够保存一下文件;

2) 倒角之后查看连线无直角和锐角。

7.4. 仿真验证

在PCB设计过程中需要对有规则约束的项都进行验证,确保验证结果与实际要求一致,裕量需要在允许的范围之内。

提取实际的走线拓扑结构,验证前仿真结果,做裕量分析,验证内容参见下表。

验证项及验证内容表

| 分类 | 验证项目 | 验证内容 | 裕量验证 |

| SI | 过冲 | 上升沿过冲、下降沿过冲 | √ |

| 下冲 | 上升沿下冲、下降沿下冲 | √ | |

| 串扰 | 串扰幅度、串扰峰值 | √ | |

| SSN | 实际开关噪声幅度 | √ | |

| Timing | 最小First Switch | 最小上升沿时的First Switch 、最小下降沿时的First Switch | √ |

| 最大Final Sette | 最大上升沿时的Final Sette 、最大下降沿时的 Final Sette | √ | |

| 建立时间 | 实际的建立时间 | √ | |

| 保持时间 | 实际的保持时间 | √ | |

| Routing | 拓扑结构 | 实际拓扑与规则的符合情况、Stub长度 | √ |

| 阻抗 | 实际阻抗 | √ | |

| 传播延迟 | 最大传播延迟、最小传播延迟 | √ | |

| 网络布线长度 | 最大网络布线长度、最小网络布线长度 | √ | |

| 相对传播延迟 | 实际管脚对相对传播延迟与规则符合情况 | √ |

8.1. 质量保证活动

8.1.1. 自检活动

布局完成后,设计者应进行自检,并将自检出的问题进行正确处理,并在PCB投板流程上经过确认方可进入PCB布线设计阶段。

投板前设计者必须进行自检,并将自检出的问题进行正确处理,在处理过程中有不能单独确定的问题时应与相关人员沟通解决。

关于自检的相关规定请见自检工作监控办法。

8.1.2. 组内QA审查

组内QA在收到投板流程后,首先确认设计者已进行充分自检,如未完成处理则返回流程,要求设计者完成后再次提交流程。

组内QA检查使用最新统一发布的《PCB投板评审要素表》,审查并记录审查结果、处理意见等。审查不通过时将流程返回设计者。

组内QA审查意见同时要填入单板设计评审记录数据库中。

8.1.3. 短路断路问题检查

1) 有单点接地;平面层挖空;修改焊盘花焊盘热焊盘的处理时,要谨慎,并把处理结果写到设计档案的地源地分割中,有利于自检和QA审查以及下一次改板。

2) P软件的电地层作负分割时,必须仔细检查。用P软件电地层负片的检查方法如下:将被分配到同一层的PLANE NET设置为不同的颜色。

只显示要检查层的全部要素。

查看有无网络跨分割区的情况(不同颜色在同一分割区),如果无则表示分割成功。

如果有跨分割的情况发生则需要编辑跨区的焊盘和过孔的PLANE THERMAL属性,使其在该区域不产生花盘,然后再通过布线保证其连通性。

3) 有开窗或开槽地方一定要加走线禁布区,防止将走线到挖断,造成断路。结构要素图中定义的禁布区同样要满足要求。

4) 必须设置正确DRC,并打开所有DRC检查。

8.2. 流程数据填写和文件提交

8.2.1. 投板流程中填写的项目

投板流程中填写的项目表

| 板名(全称): | 版本号: | ||

| 数量(请考虑中试对PCB板的需求数量): | 拼版: | ||

| 板框面积(长度)cm: | 板框面积(宽度)cm: | ||

| 层数: | 厚度mm: | ||

| 菲林张数: | 非电源地网络连接数: | ||

| □普通板 | 此6类中至少选其中一项,可多选,并留出意见域。 | □阻抗控制要求 | 选是后必填 |

| □机械埋盲孔板 | □特殊板材和规格 | 选是后必填 | |

| □射频板 | 最小线宽/线间距 | 必填 | |

| □ HDI板(1+n+1) | 纵横比 | 必填 | |

| □ HDI板(2+n+2) | 表面处理 | 必填 | |

| □其它 | 设计周期(工作日): |

注:

1) 版本号栏填写纯版本号,如“1”、“2”、“1 REV.A”等;

2) 如是拼版,板框的长度、宽度数据填写拼版后的尺寸;

3) 数量栏填写拼版前的单板需求数;

4) 拼版栏填写拼版后的单元数,如2×3拼版的情况,则填写6;

5) 设计周期栏填写设计者实际在该设计任务上投入的工作日数。

8.2.2. 投板流程上粘贴2个压缩文件

PCB设计文件(*PCB文件名*.zip)

单板设计要求文件(*PCB文件名*.txt)

9.1. 信号质量测试工程师具备的知识

作为信号质量测试工程师,应该有下面三个方面的知识:

1) 首先要对测量工具(示波器)有清楚的了解,要了解示波器的性能,掌握示波器及其探头的使用,清楚信号质量异常的测试与示波器菜单设置间的配合关系。

2) 对异常的信号形式有全面和清楚的认识,对异常信号的异常指标有了解。

3) 对被测单板的原理电路有一定的认识和了解,要求能够对信号进行分类,了解板上的关键器件、关键总线、关键信号的信号质量要求和相关时序参数。

9.2. 测试目的及测试内容

利用示波器测试的结果,来验证仿真分析结果的正确性和验证仿真模型(IBIS或HSPICE)的准确度,为提高今后分析仿真精度提供依据,同时对被测信号的质量进行评估,分析存在的问题,采取相应的措施,以提高单板性能、稳定性和可靠性。

信号完整性测试内容主要针对单板和系统中各数字处理部分信号进行测试(包括信号质量测试及关键总线的时序测试),以便与分析仿真结果进行比较,同时也包括对没有进行SI分析仿真的信号,如重要专用芯片的输入输出信号、时钟产生与合成电路的输入参考源信号、输出时钟信号、时钟反馈信号、复位电路输入输出的复位信号、和有关控制信号等其他信号进行测试,针对存在的信号质量问题,采用信号完整性分析原理进行分析,提出消除和改进措施。

9.3. 测试方法

9.3.1. 示波器及探头的选择与使用

1) 示波器应选择带宽高于500MHz的数字示波器及示波器配用探头(Tektronix TDS754A配Tek P6139A 探头,推荐使用TDS754或以上的示波器)。

2) 当测试信号上升下降时间<2ns时,应选择带宽为1GHz以上的数字示波器及配用有源探头(如Tektronix TDS784A配P6245探头)。

3) 测量差分信号时尽量选用差分探头(如Tektronix P6247探头)。 差分探头能够测量的差分电压范围是有限的。例如,差分探头P6247,其上的开关打在÷10档位时,能测的差分电压范围是±8.5V,打在÷1档位时只有±850mV。差分信号峰峰值超过850mV时(比如测公司常用的平衡线传输信号±5V),要注意选用÷10档,否则会因输入过大而使显示的波形发生错误。差分探头所能承受的共模电压也是有限的,超过此值时,会发生测试结果错误,甚至损坏探头。差分探头上一般都标有其能承受的共模电压,测试时要注意这一点。

4) 使用示波器探头的原则:地线尽量短,探头直接点在被测信号管脚或附近的测试点上,探头与探头地线形成的回路要小并且尽量与PCB板相垂直; 多个探头不能共用同一地线,多个探头本体连线之间要保持一定的距离,不能并排在一起,也不能绞在一起。

5) 注意测试信号的幅度不要超过示波器和探头的安全范围,以免测试失真和造成设备损坏。 不允许在探头还连接着被测试电路时插拔探头。

6) 示波器档位的使用(以Tektronix TDS754A为例)

测量上升沿,上升沿过冲,上升沿回冲时,示波器触发开关置于“上升沿”触发,触发电平置于“50%”处,垂直幅度开关可置于“2.00V”,水平时间开关置于“M50.00ns”,选择示波器MEASURE中的菜单测量上升沿时间,过冲及回冲高度。或者可选用Instavu功能,使用cursor菜单中的V Bar进行手动的测量。

测量毛刺时,选示波器触发菜单“TYPE”中的“pulse”(脉冲触发),调节Polarity & width及触发电平可设定捕捉毛刺的宽度与幅度。Polarity &width(触发宽度)根据毛刺的实际宽度选择,触发电平根据毛刺的实际伏值选择。幅度及时间刻度与上相同。

7) 使用示波器的InstaVu(长余辉)功能

Tek示波器提供了InstaVu功能,用于发现信号异常,低电平毛刺高数据信号眼图异常及高电平低。其机理在于可以将时间轴上的波形连续采样显示,而不象普通模式那样使用采样—处理—采样的工作方式,避免了处理周期中波形丢失的情况。同时Instavu还可以将较长时间波形叠加显示,方便观察波形抖动。

使用时首先在普通测试方式下,将波形显示出来,显示一两个信号周期。随后使用示波器的InstaVu键进入长余辉显示方式,调整“Display”中的余辉显示时间为2 .00s左右。如果发现在信号的高低电平稳定期间有余辉闪动,该信号异常。可根据余辉的形式(毛刺或信号跳变沿问题)返回普通测试方式下,选用正确的触发方式进一步详细测试。

8) 使用采样示波器的TDR功能

测试PCB板上传输线的特性阻抗是可使用带TDR功能的示波器如Tektronix公司的数字采样示波器11801C。这里以11801C示波器为例说明其使用方法:

11801C示波器具有TDR的测试功能,它需与SD-24采样模块配合使用。SD-24为具有TDR功能的双通道采样模块,它的带宽为20GHz,反射上升时间为35nS。待测的PCB上的传输线需要用SMA插座引出,待测PCB板上的传输线的长度应在4000mil以上,以提高测试精度。测试步骤如下:

将示波器11801C初始化:按"UTILITY"按钮,触摸屏上的"Initialize",在弹出的框中再次触摸"Initialize"。

将具有SMA头的电缆(延迟时间最好为5nS)一端接采样头SD-24的任一输入端,电缆的另一端接待测传输线的SMA插座。注意待测PCB板不要通电。

选择采样通道:按一下采样头上连接电缆通道的'SELECT CHANNEL'按钮。

打开示波器的TDR功能:按一下示波器上的菜单按钮"WAVEFORM",触摸屏上的"Sampling head Fun's"选项,在弹出的框中触摸"TDR Preset"。

调整横坐标和纵坐标的分辨率,并配合左右移动和上下移动功能,使待测特性阻抗点移动到显示屏上易于观察的适当位置。

选择横坐标和纵坐标的单位:在菜单按钮"WAVEFORM"下,触摸屏上的"Graticules"选项,将弹出的框中Y轴的单位选为Rho,触摸"Exit"离开该弹出式菜单。

选择测试点进行测试:触摸屏上的"Cursors"图标,将有两个光标出现,调整示波器上的旋钮(两个旋钮各对应一个光标)使光标沿着采样波形移动到被测传输线所对应的点。

读出被测传输线的特性阻抗:在显示屏下半部分"Cursor"对应的框中有关于测试点的信息,读取![]() (或

(或![]() )对应于

)对应于![]() 下的值即为被测点的特性阻抗。

下的值即为被测点的特性阻抗。

对于差分传输线的特性阻抗的测试方法与上面介绍的方法相似,只是需要两根具有SMA头的电缆(尽量等长),分别连接被测的差分线对和采样头的两输入端,并在步骤(4)中,在"Samplinghead Fun's"的弹出菜单中触摸"DiffTDR Preset",打开示波器的差分TDR功能。

9.3.2. 信号波形参数定义

Ø 信号波形参数的概念

图9-3-1 信号波形参数的概念图

资料表明,信号波形参数实际发生的问题形式很多,根据目前工作的结论,信号质量常见的问题主要表现在五个方面:过冲,回冲,毛刺,边沿,电平。

Ø 导致信号波形问题的一般原因

1)过冲

图9-3-2 过冲图

过冲带来的问题是容易造成器件损坏,过冲过大也容易对周围的信号造成串扰。造成过冲大的原因是不匹配,消除的方法有始端串电阻或末端并阻抗(或电阻)。

2)毛刺

图9-3-3 毛刺图

毛刺作用在高速器件上,容易造成误触发、控制信号控制错误或时钟信号相位发生错误等问题,毛刺脉冲带来的问题多发生在单板工作不稳定或器件替代后出现问题。造成毛刺的原因很多,比如逻辑冒险,串扰、地线反弹等,其消除的方法也不尽相同。

3)边沿

图9-3-4 边沿图

边沿速度缓慢发生在信号线上时,会造成数据采样错误。其产生原因通常是输出端容性负载过大(负载数量过多),输出是三态时充(放)电电流小等原因。

4)回冲

图9-3-5 回冲图

回冲产生的原因是信号线不匹配或多负载等原因,消除的方法是加匹配电阻或调整总线的拓扑结构。

5)电平

图9-3-6 电平图

输入电平幅度不符合要求时,会造成器件输出错误。导致电平异常的原因主要有:输出过载,电平不匹配,三态总线、总线冲突等原因。

9.3.3. 测试点的选择原则

1) 在PCB布线阶段就要求开发人员预留关键信号的测试孔,同时在板上各部分均匀地布上适宜数量的地孔以方便测试。测试时尽量控制地线引出线的长度。

2) 因为传输线效应的影响,探针的位置和需要测试的管脚位置越远,波形相差就越大。 首先选择探头直接搭在接收器件信号的IC引脚上测试信号(不会引起短路),对于BGA及细小管脚的SMT器件引脚,则选择最靠近接收器件信号管脚的信号线上的过孔(或测试孔)进行测试。

3) 对有时序测量要求的网络应同时在发送和接收器件的时钟和信号网络的管脚附近放置测试孔,以便测试信号的相关时序参数。

4) 对有阻抗测试要求的单板,在PCB设计时建议在控制阻抗的信号层的空白区布1根(单线)或2根(差分线)大于4inch的线,并用SMA插座引出以便测试使用。

9.3.4. 信号质量测试应覆盖各功能块的信号

通常应考虑测试以下各功能模块(由于传输线效应,同一个信号网络在不同的拓朴点上,其信号质量差异很大,故一般要求该网络上所有输入点的信号质量必须分别进行测试)。

1) 组合逻辑电路输入、输出的重要逻辑控制信号。

2) 微处理器单元电路:A.读写信号;B.地址数据信号;C.片选信号;D.输入时钟信号;E.中断控制信号;F.其它控制信号;

3) 双端口RAM:A.读写信号;B.地址数据信号;C.选通信号;D.RDY信号

4) 专用芯片的各类重要输入输出信号。

5) 时钟产生与合成电路:A.输入参考源信号;B.输出时钟信号;C.时钟反馈信号;

6) 复位电路输入输出的复位信号;

7) 其他信号。

9.3.5. 各类信号的重点测试项目

Ø 时钟信号测试项

1) 边沿单调性和上升下降时间;

2) 高电平过冲和低电平过冲;

3) 最低高电平和最高低电平;

4) 相位(skew)和抖动;

5) 占空比;

6) 毛刺。

Ø 数据地址信号测试项

1) 高电平过冲和低电平过冲;

2) 最低高电平和最高低电平;

3) 上升下降时间;

4) 毛刺;

5) 高低电平回冲。

Ø 电平控制信号测试项;

1) 高电平过冲和低电平过冲;

2) 最低高电平和最高低电平;

3) 上升下降时间;

4) 工作电平脉宽;

5) 毛刺;

6) 高低电平回冲。

Ø 边沿控制信号测试项

1) 边沿单调性和上升下降时间;

2) 高电平过冲和低电平过冲;

3) 最低高电平和最高低电平;

4) 毛刺。

Ø 差分传输信号测试项

1) 差分信号边沿单调性和上升/下降时间(差分时钟信号);

2) 差分信号最低高电平和最高低电平;

3) 单端信号共模电压Vos;

4) 单端信号最低高电平和最高低电平;

5) 高速差分信号眼图测试。

Ø 同步总线的时序测试

1) 发送器件的输出有效时间;

2) 发送器件的输出保持时间;

3) 接收器件的输入建立时间;

4) 接收器件的输入保持时间。

Ø 异步总线的时序测试

因异步总线的时序要求因器件而异,请结合器件具体时序图和相应时序参数进行测试。

9.3.6. 各类信号测试方法和注意事项

为了正确地用示波器去观察一个信号的波形。通常在开始测试时可以适当将垂直分辨率和水平适当调小,以便观测信号波形的全貌,如果对波形的某个细节(如时钟信号的上升沿)感兴趣,可以再适当调整水平时基和垂直幅度分辨率去观察波形的细节。当需要对IBIS模型进行验证时,一定要将波形放大去观察上升沿和下降沿的细节部分。

Ø 时钟信号

时钟信号对边沿的要求严格,一般情况下高速时钟多为点到点驱动,少数也有一驱多的情况。时钟信号为单向信号,测试时必须选择在终端进行测试,对一驱多的负载必须对每一个终端负载分别进行测试以观察信号质量是否符合要求。

Ø 地址信号、控制信号等单向传输信号

需要在信号的接收端测试信号质量,特别是对于多负载的地址信号、控制信号等单向传输信号,需要在各个负载处分别测试;对于控制信号必须制造条件使其发生跳变,测试其跳变时的波形。

Ø 数据总线等双向传输信号

需要对总线上的各个芯片分别进行信号质量测试。因为多负载的双向总线,总线上的各个芯片都可能发送信号,由于传输线效应,此时其他各个接收芯片处的波形也各不相同,因此测试时要有这样的意识,测试需要覆盖各种可能的信号流向,并在各个接收芯片处分别测试,而不是仅仅简单的在一个芯片处随意测试一个波形。特别是当需要对仿真结果进行验证时,要确保仿真和测试的信号流向及测试点都需要保持一致。

Ø 背板接口信号

对于背板接口信号的信号质量测试,要注意针对单板特有配置情况进行专向的测试。

单板在各种负荷下测试,测试那些会因驱动负载不同而改变的信号:A.轻载;B.满载;C.过载。例如:驱动板输出1驱4的时钟信号给不同槽位,在进行单板输入时钟信号测试时,就要在1块板、2块板负载、3块板负载、4块板负载的条件下测试输入信号;

单板与驱动板不同位置:A.最接近驱动板的槽位;B.最远离驱动板的槽位;C 其他中间槽位。对于重要的驱动信号,通常要求每个槽位都必须进行重要输入信号质量的测试;

主备工作(热备份)方式,对单板主备倒换瞬间,板与板的接口信号波形进行测量。

Ø 接口差分驱动输入输出信号线

这些信号主要集中在不同信号框之间的传输信号上,经常出现的问题是两差分输入电平差不满足信号电平差的要求。应选用差分探头进行差分信号的测试,探头的两端分别连在差分信号的正负信号端,探头的保护地连在单板的地线上,测试差分正负端信号经过差分后的波形。另外还应将探头的一端及探头的保护地连在单板的地线上,另一端连在差分正或负端信号线上,测试正负端信号各自的单边对地电压。

Ø 同步总线的时序测试

对于同步总线,最重要的四个时序参数就是:

1)发送器件的输出有效时间;

2)发送器件的输出保持时间;

3)接收器件的输入建立时间;

4)接收器件的输入保持时间。

其中发送器件的输出有效时间和输出保持时间是由输出器件的自身特性决定的,而与系统的设计无关,而接收器件的输入建立时间和输入保持时间是由设计决定的,设计需要确保这两个时序参数符合接收器件的时序要求,因此接收器件的输入建立时间和输入保持时间是同步总线时序测试的重点。

对于地址、控制总线这些单向传输信号,可以仅仅在信号的接收端测试信号的建立时间和保持时间,当有多个负载时,考虑传输线的效应,需要针对各个接收器件分别测试建立时间和保持时间,并分别与接收器件的时序参数向比较看其是否符合要求并留有一定的裕量。

对于数据总线等双向传输信号,时序测试时可通过辅助测试程序控制数据信号的流向(只读或只写),分别对读和写时的时序参数进行测试。也可以不需要特殊的测试程序,此时需要通过用示波器监视读写和片选等控制信号,来获知某时刻数据总线上的信号流向。

同步总线(地址、数据、控制总线)在PCB上往往具有相似的拓扑结构,由于PCB的走线密度越来越高,总线的相互间距不可能很大,并且往往长距离并行走线,同步串扰不可避免,考虑串扰和地弹噪声,同步总线(地址、数据、控制总线)上往往会产生较大的毛刺,如毛刺的大小超过了高、低电平的门槛电压,并非一定会对系统的正常工作造成影响,如何判断其是否会对总线的正常操作造成影响呢?这也需要结合时钟信号进行时序测试,关键是看超过门槛电压的毛刺信号是否落入总线相对于时钟信号的有效采样范围。

10.1.测试验证过程附录

10.1.1.同步总线时序测试实例参考

Ø 发送器件的输出有效时间参数测试

对于某单板的某同步总线上的某信号,其为高电平有效,测试点选择在发送器件的管脚处或最近的一个过孔,发送器件的输出有效时间参数测试波形如下图所示。通道1为发送器件的参考时钟,参考点选择在时钟的有效沿(本例为上升沿)的VCC/2处(对于3.3V器件为1.6V左右);通道2为被测信号,参考点选择在测试信号上升沿的一半幅度处(不包括回沟后面的部分)。

图10-8-1 发送器件的输出有效时间参数测试

Ø 发送器件的输出保持时间参数测试

对于某单板的某同步总线上的某信号,其为高电平有效,测试点选择在发送器件的管脚处或最近的一个过孔,发送器件的输出保持时间参数测试波形如下图所示。通道1为发送器件的参考时钟,参考点选择在时钟的有效沿(本例为上升沿)的VCC/2处(对于3.3V器件为1.6V左右);通道2为被测信号,参考点选择在测试信号下降沿的一半幅度处(不包括回沟后面的部分)。

图10-8-2 发送器件的输出保持时间参数测试(下降沿)

Ø 接收器件的输入建立时间参数测试

对于某单板的某同步总线上的某信号,其为高电平有效,测试点选择在接收器件的管脚处或最近的一个过孔,接收器件的输入建立时间参数测试波形如下所示。通道1为接收器件的参考时钟,参考点选择在时钟的有效沿(本例为上升沿)的VCC/2处(对于3.3V器件为1.6V左右);通道2为被测信号,参考点选择在上升沿的高电平的门槛电压处(3.3V的CMOS器件为2V),且参考点之后波形不会回落到高电平的门槛电压以下。

图10-8-3 接收器件的输入建立时间参数测试

Ø 接收器件的输入保持时间参数测试

对于某单板的某同步总线上的某信号,其为高电平有效,测试点选择在接收器件的管脚处或最近的一个过孔,接收器件的输入保持时间参数测试波形如下所示。通道1为接收器件的参考时钟,参考点选择在时钟的有效沿(本例为上升沿)的VCC/2处(对于3.3V器件为1.6V左右);通道2为被测信号,参考点选择在下降沿的高电平的门槛电压处(3.3V的CMOS器件为2V)。

图10-8-4 接收器件的输入保持时间参数测试

10.1.2.示波器和探头带宽对测试信号边沿的影响

信号从某器件的输入管脚流入再从其输出管脚流出都将增加延迟,在《 High speed digital design: a Handbook of Black Magic Dr. Howard Johnson》一书中给出如下计算公式:

即当上升沿时间为T1的信号在经过N-1个设备后,其最终输出信号的上升时间为Trise composite。那么,当上升沿时间为T1的被测信号,在经过探头和示波器后,最终显示的波形的上升时间如下图所示:

图10-8-5 实际信号经过探头和示波器的响应过程图

对满足3dB带宽的测试设备和满足RMS带宽的测试设备,其转换时间分别如公式(2)和(3);

T=0.338/F3dB --------- (2)

T=0.361/FRMS--------(3)

通常示波器和探头提供3dB带宽指标,若带宽都是500M的示波器和探头在测量上升时间为2ns的信号时,显示的信号上升时间为:

T1=2ns

T2=T3=0.338/500M=0.676ns

Tdisplay=(22+0.676 2+0.676 2) 1/2=2.217ns

若带宽都是2G的示波器和探头在测量上升时间为2ns的信号时,显示的信号上升时间为:

T1=2ns

T2=T3=0.338/2G=0.169ns

Tdisplay=(22+0.169 2+0.169 2) 1/2=2.014ns

可见,在测试高速信号时要使测试精度提高的话,应尽量选择高带宽的示波器和探头。

10.1.3.测试探头的地回路对测试信号的影响

对一个实际的测试探头,当测试信号点到接地点的距离为1英寸,探头的接地回路线为3英寸,假设其输入电容为10pF和输入阻抗为10M欧时,由测试信号、探头接地回路和测试仪构成的等效短路模型如图3所示。

图10-8-6 测试信号、探头接地回路和测试仪器构成的等效电路图

而由接地线(线直径为0.02英寸的(AWG)24线)回路构成的电感值为:

而由接地回路电感和输入电容构成的双极点电路的上升时间常数可表示为(5)式。T10-90 = 3.4 TLC =4.8nS ----------(5)

从(5)式中看到,即使探头的带宽较宽(300MHz,对应的上升时间为1.1nS),但在3英寸长的接地回路条件下,它测试信号边沿已经衰减为4.8nS,可见探头和示波器寄生参数对信号的巨大影响。

在图(3)中,我们还看到,接地回路的电感L和测试仪的输入电容构成谐振电路。在测试信号输出内阻为Rs,其谐振因子Q可近似表示为:

Q -----------(6)

从(6)式中得知,当信号的输出电阻较小,而接地回路的寄生电感较大时,可形成较大的谐振因子Q,造成测试信号的振铃和过冲现象。

下表中给出不同接地回路电感和不同输入电容探头对测试信号边沿的衰减和在不同信号种类下的谐振因子表(TTL的RS=30 Ohm;ECL的RS=10 Ohm)。

不同接地回路电感和不同输入电容探头对测试信号边沿的衰减和在不同信号种类下的谐振因子表(引自Dr. HowardJohnson High speed digital design: a Handbookof Black Magic)。

| 接地回路电感(nH) | 10pF探头 | 2pF探头 | ||||

| T10-90(nS) | QTTL | QECL | T10-90(nS) | QTTL | QECL | |

| 200 | 4.8 | 4.7 | 14.1 | 2.15 | 10.5 | 31.6 |

| 100 | 3.4 | 3.3 | 10 | 1.52 | 7.4 | 22.3 |

| 30 | 1.9 | 1.8 | 5.4 | 0.83 | 4.1 | 12.2 |

| 10 | 1.1 | 1.1 | 3.2 | 0.48 | 2.4 | 7.1 |

| 3 | 0.6 | 0.6 | 1.7 | 0.26 | 1.3 | 3.9 |

| 1 | 0.3 | 0.3 | 1 | 0.15 | 0.7 | 2.2 |

从上表可清楚看出,探头接地回路寄生电感和和输入电容越小,对测试信号边沿的影响也越小。而对测试信号幅度,则是接地回路电感越大,影响也越大;输入电容越大,影响越小,但是接地回路电感的影响比输入电容对信号过冲的影响要大得多。

10.1.4.高速差分眼图测试方法

对于高速收发器、光接收器及部分标准接口,很多示波器都提供有眼图模板来套用如155M、622M、1.5G眼图模板等。但更高速率的收发器如2.5G、3.125G等在示波器中没有模板,根据系统误码率指标可按如下方法确定测试模板。

以CML差分电平为例,其差分电平的幅度不小于200mV,若抖动不超过单位数据位的40%,也就是400ps×40%=160ps。由一个数据位的宽度减去两边抖动的大小,可得到眼图对抖动的要求为:400-2×160=80ps。由此,可得到一个最小眼图模板如下图所示:

图10-8-7 最小眼图模板

若为保证误码率小于10E-12要求,要求信号眼图进入模板的概率小于10E-12,考虑信号边沿有随即抖动,抖动符合正态分布,根据正态分布的概率积分函数。当1-Φ(x)<10E-12 时,可以计算出信号边缘落在距离理论期望位置7.03s之外的概率为10E-12,由此可以计算出信号RMS抖动不能超过22.76ps。即7.03σ<400×40%ps。

图10-8-8 抖动分布图

一般作眼图测试,由于测试时间不可能很长,按照2KHITS计算,信号的PK—PK抖动一般略大于3.4s ,由此可以计算出,为保证误码率指标,需要的眼图模板的裕量为3.4s 。即400-3.4s×2=245ps。

在Y方向,模板主要关心噪声裕量,一般可取100mV,则得到的眼图模板即可保证小于10E-12的误码率及100mV的差分噪声裕量。由此得到的眼图模板如下图所示:

图10-8-9 实际测试用眼图模板

应当说明的是,以上基于概率统计分析的结果只是一个充分条件,并非必要条件,是一个比较苛刻的理想测试规范。