定点运算器部件

基本的二进制加法/减法器

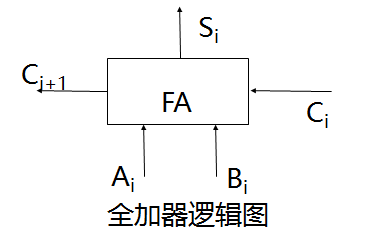

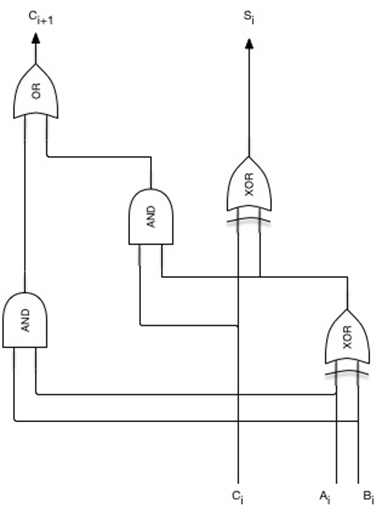

在计算机中完成两个二进制数相加的基本加法器有半加器和全加器。半加器在完成两数相加时,不需要考虑低位进位。全加器用来完成两个二进制数相加,并且同时考虑低位的进位,即全加器完成三个一位数相加的功能。设:

Ai 表示被加数的第i位

Bi 表示加数的第i位

Ci 为第i-1位向第i位产生的进位

Ci+1 为第i位向第i+1位产生的进位

Si 为第i位产生的和

则全加器以Ai、Bi、Ci为输入,以Ci+1、Si为输出构成一个逻辑图。

图3.4-1 全加器的逻辑图

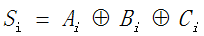

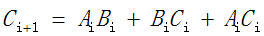

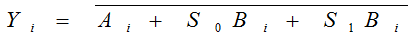

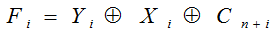

全加器的表达式为:

图3.4-2 全加器的逻辑实现图

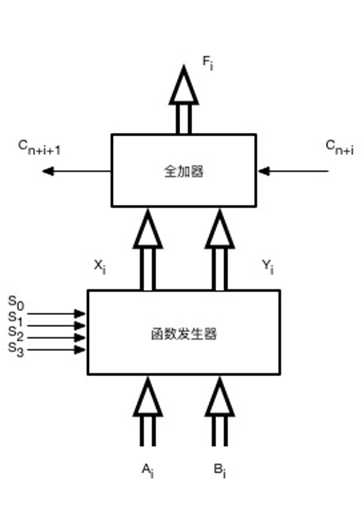

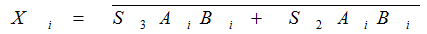

算术逻辑运算单元的基本思想

为了将全加器的功能进行扩展以完成多种算术逻辑运算,我们先不将输入Ai和Bi和下一位的进位Ci直接进行全加,而是将Ai和Bi先组合有控制S0,S1,S2,S3控制的组合函数Xi和Yi,然后再将Xi,Yi和下一位进位数通过全加器进行全加,这样,不同的控制参数可以得到不同的组合函数,以能够实现多种算术运算和逻辑运算。

图3.4-3 ALU的逻辑结构原理框图

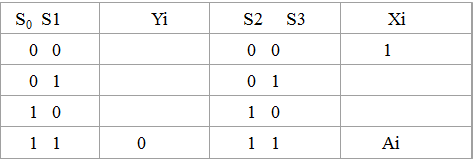

表3.4-1 Xi、Yi与控制参数和输入量的关系

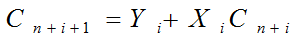

ALU的某一位逻辑表达式如下:

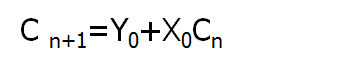

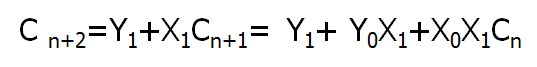

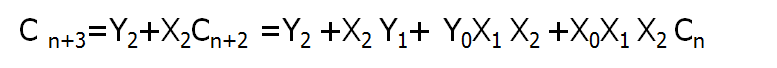

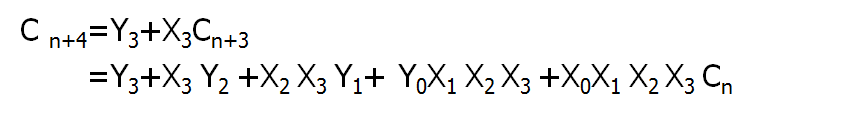

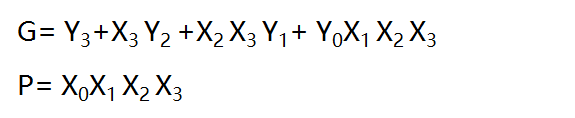

每一位的进位公式可递推如下:

设:

则:

其中:G称为进位发生函数

P称为进位传送函数

该式表明,第0位的进位输入可以直接传送到最高进位位上去,因而可以实现高速运算。

加法器

1. 串行加法:从低位开始,每步只完成一位运算的加法。

串行加法器只需要一个全加器和一个进位触发器,计算两个n位数之和,需要n+1步(1位符号位),或n+2步(2位符号位)运算。高位运算只有等低位运算完成后才能进行,速度较慢

2. 并行加法器:可在同一时刻完成 n 位数的运算。

若采用变形补码表示一个机器数,则符号位需2位,这时需要 n+2 个加法器。运算速度比串行进位加法器高很多,这是用足够多的硬件设备换来的。

3. 并行加法器进位传递方式和传递时间

(1)串行进位方式:每一级进位直接依赖于前一级的进位,即进位信号是逐级形成的。

假设,一级“与门”、“或门”的延迟时间为ty, 则每一级进位的延迟时间为2ty。在字长为n位的情况下,C0→Cn的最长延迟时间为2nty。所以,串行进位速度慢,且加法器位数越长,进位延迟时间越长。

(2)并行进位方式

(3)分组并行进位方式

A. 一级分组先行进位法

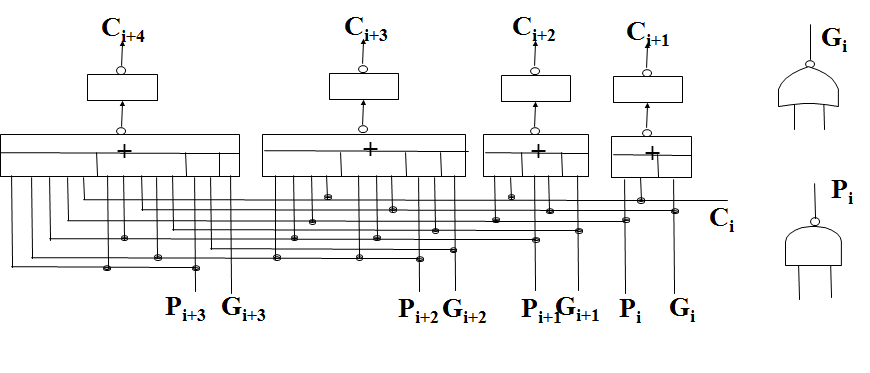

相邻4位加法器单元逻辑(第i-1, i-2, i-3 ,i-4位)

Ci=Gi+PiCi-1

Ci-1=Gi-1+Pi-1Ci-2

Ci-2=Gi-2+Pi-2Ci-3

Ci-3=Gi-3+Pi-3Ci-4

展开:

Ci-3=Gi-3+Pi-3Ci-4

Ci-2=Gi-2+Pi-2Gi-3+ Pi-2Pi-3 Ci-4

Ci-1=Gi-1+Pi-1 Gi-1+ Pi-1Pi-2Gi-3+ Pi-1 Pi-2Pi-3 Ci-4

Ci=Gi+PiGi-1+Pi Pi-1 Gi-2+Pi Pi-1 Pi-2Gi-3

+ PiPi-1 Pi-2Pi-3 Ci-4

若:Ci中前四项记为GI*,最后一项的前四个因子记为PI*,

则 则:Ci= GI*+ PI* Ci-4

图3.4-4 成组先行进位部件CLA的逻辑电路图

图3.4-5 全先行进位逻辑级联组成的ALU

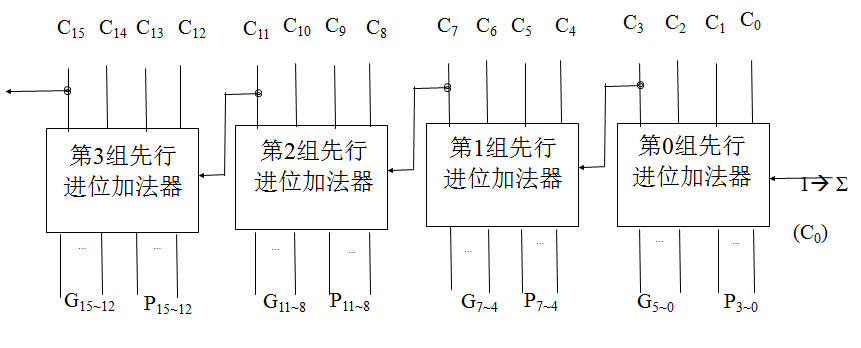

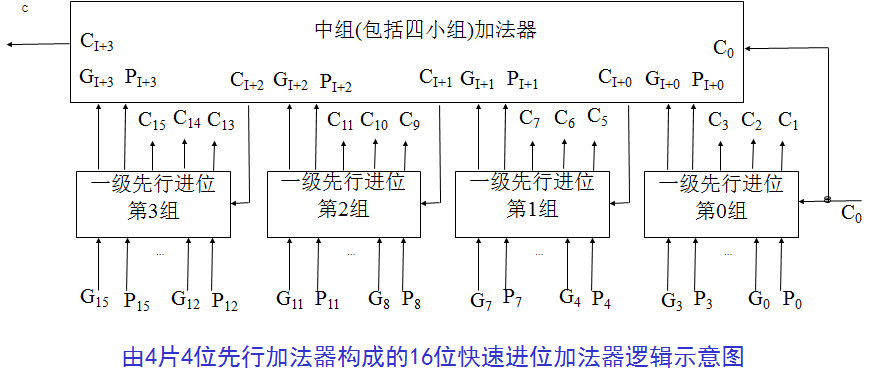

B. 二级分组先行进位法

仿一级分析法

C3= G3*+ P3*(1àΣ)

C7 = G7*+ P7* G3*+ P7*P3*(1àΣ)

C11 = G11*+ P11* G7*+ P11*P7* G3*+ P11*P7*P3*(1àΣ)

C15 = G15*+ P15* G11*+ P15* P11* G7*+P15*P11* P7* G3*

+

P15*P11*P7*P3*(1àΣ)

图3.4-6 由4片4位先行加法器构成的16位快速进位加法器逻辑示意图

定点运算器的逻辑结构

运算器包括ALU、阵列乘除器、寄存器、多路开关、三态缓冲器、数据总线等逻辑部件。计算机的运算器的结构一般有三种。分别是单总线结构的运算器、双总线结构的运算器和三总线结构的运算器。

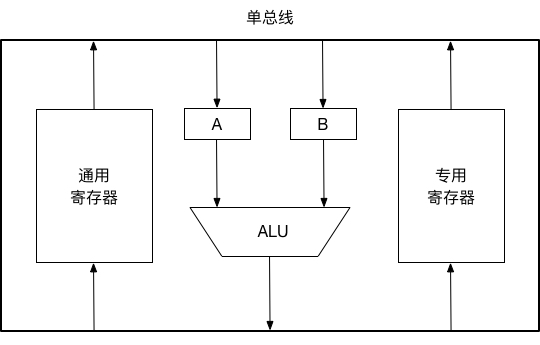

(1)单总线结构的运算器

输入数据和操作结构需要三次串行的选通操作,但它并不会对每种指令都增加很多执行时间。由于只控制一条总线,所以控制电路比较简单。

图3.4-7 单总线结构的运算器

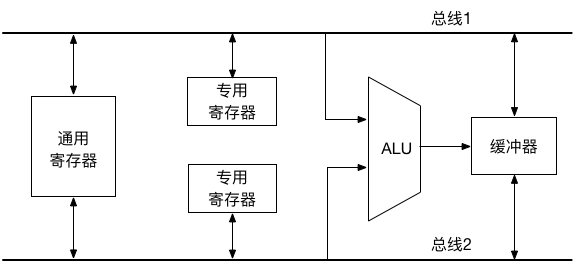

(2)双总线结构的运算器

在这种结构中, 两个操作数同时加到ALU进行运算,只需要一次操作控制, 而且马上就可以得到运算结果。两条总线各自把其数据送至ALU的输入端。专用寄存器分为两组,它们分别与一条总线交换数据。 这样,通用寄存器中的数据就可以进入到任一组专用寄存器中去, 从而使数据传送更为灵活。

ALU的输出不能直接加到总线上,这是因为, 当形成操作结果的输出时, 两条总线都被输入数占据, 因而必须在ALU输出端设置缓冲寄存器。

图3.4-8 双总线结构的运算器

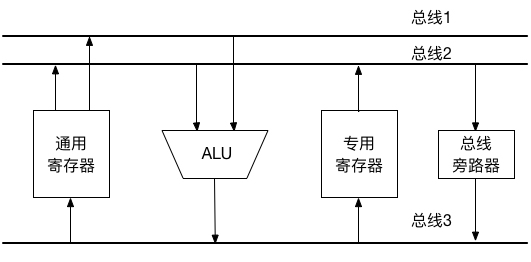

(3)三总线结构的运算器

在三总线结构中,ALU的两个输入端分别由两条总线供给,而ALU的输出则与第三条总线相连。这样,算术逻辑操作就可以在一步的控制之内完成。 由于ALU本身有时间延迟,所以打入输出结果的选通脉冲必须考虑到包括这个延迟。另外,设置一个总线旁路器(桥)。如果一个操作数不需要修改, 而直接从总线2传送到总线3, 那么可以通过总线旁路器把数据传出。

图3.4-9 三总线结构的运算器