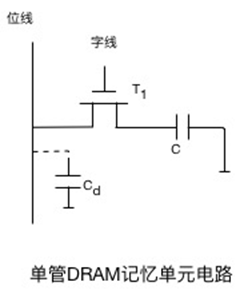

动态随机存储器DRAM

四管动态存储元

在六管静态存储元电路中,信息暂存于T1,T2管的栅极,这是因为管子总是存在着一定的电容。负载管T3,T4是为了给这些存储电荷补充电荷用的。由于MOS的栅极电阻很高,故泄漏电流很小,在一定的时间内这些信息电荷可以维持住。为了减少管子以提高集成度,把负载管T3,T4去掉,这样变成了四管的动态存储电路。

图5.2-8 4管DRAM记忆单元电路

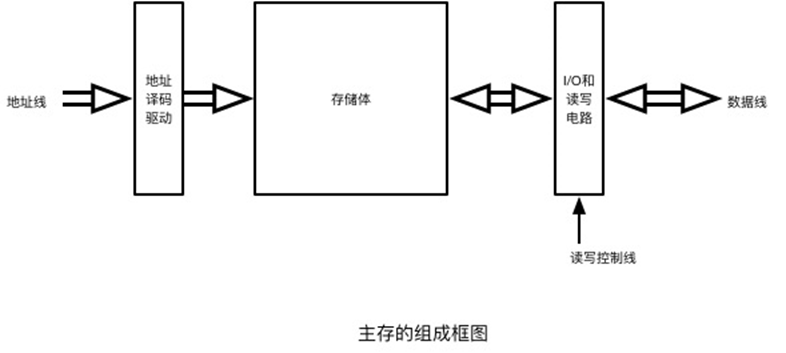

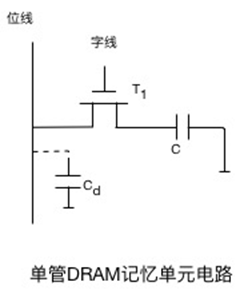

单管动态存储元

它由一个管子T1和一个电容C构成,写入时,字选择线为“1”,T1管导通,定入信息由位线(数据线)存入电荷C上的电荷,通过T1输出到数据线上,通过读出放大器即可得到存储信息。

图5.2-9 单管DRAM记忆单元电路

当字线为高电平时,该电路被选中。

写入时,若写入“1”,位线为高电平,对电容C充电;若写入“0”,位线为低电平,C上的电荷经位线泄放。

读出时,若原存“1”,C上有电荷,经T1管在位线上产生读电流,完成读“1”操作。若原存“0”,C上无电荷,在位线上不产生读电流,完成读“0”操作。当读操作完毕,存储电容C上的电荷已被泄放完,故是破坏性读出,必须采取重写(再生)的措施。

存储电容C的容量不可能做得很大,一般比位线上的寄生电容Cd 间分配,就会使读出信息减少,所以,用单管记忆单元组成的存储器中,读出放大器应有较高的灵敏度。因为信息是存储在一个很小电容C上,也只能保留几毫秒的时间,所以必须定时第进行刷新操作。

刷新

动态RAM的存储元件依靠电容上的电荷表示所存储的数据信息,而电容的绝缘电阻不可能无限大,因此漏电不可避免。每隔一定的时间就对存储体中全部的存储电进行充电,以补充所消失的电荷,维持原存信息不变,这个过程称为“刷新”。

刷新的时间间隔取决与存储电容上的电荷释放速度。应在规定的时间内对全部存储体刷新一遍。

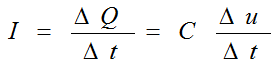

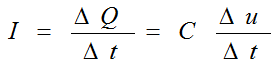

设电容为C,电压为u,电荷Q=Cu,则泄放电流为:

如果取C=0.2pF, △u=1V,I=0.1nA,则: 泄放时间△t=2ms

刷新方式:

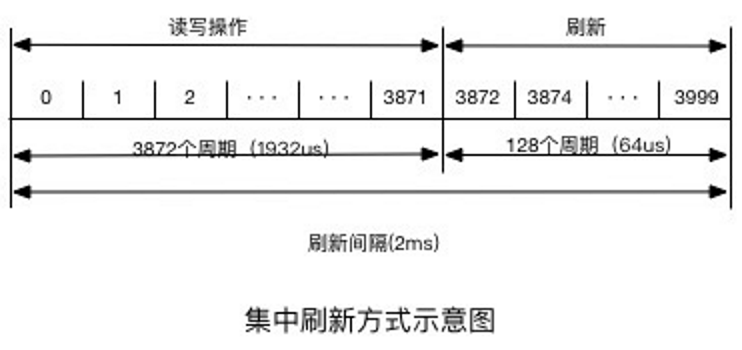

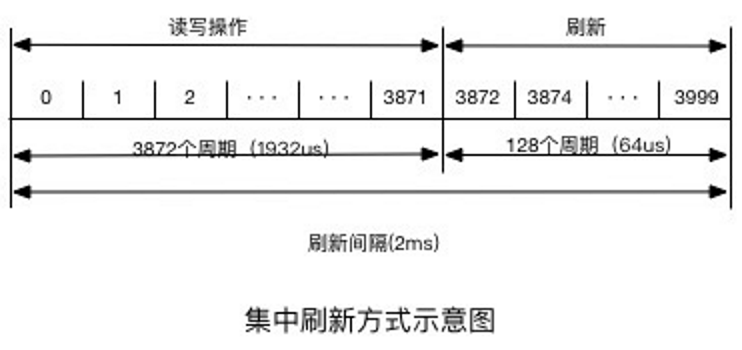

(1)集中式刷新

在整个的2MS的时间内集中对每一行进行刷新,刷新时读/写操作停止,每行的刷新一般与一次 的读/写周期相等。

刷新时间=存储矩阵行数╳刷新周期

刷新周期是刷新一行所需要的时间。由于刷新过程就是“假读”的过程,所以刷新周期等于存 取周期。

对128*128矩阵存储器进行刷新时,刷新的时间相当于128个读周期,假如读写周期为0.5us,刷新 周期为2ms,那么共有2ms/0.5us=4000个周期.其中4000-128=3872个周期用来读写或维持,然后用 128个周期,相当于128*0.5=64us用来刷新操作.由于在这64us中不进行读写操作,故称其为死时间.

图5.2-10 集中式方式示意图

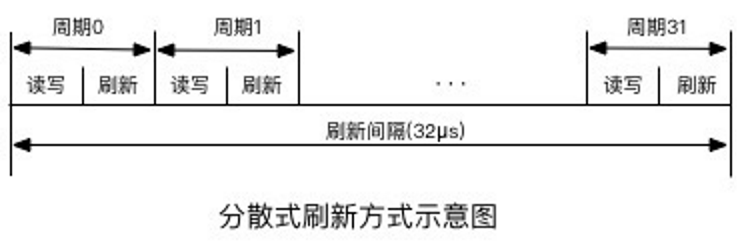

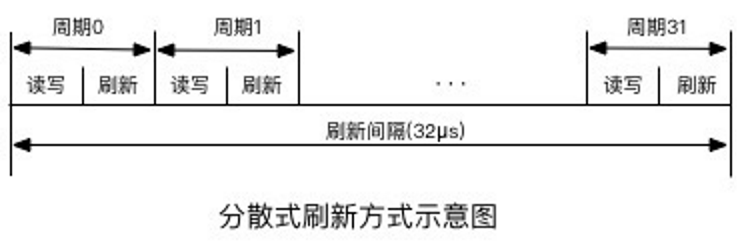

(2)分散式刷新

是把每行存储元件的刷新分散安排在各个读写周期内即把读写周期分为两段,前段表示读写,后段 表示刷新时间.

这种刷新方式增加了系统的存取周期。

这种刷新方式没有死区,明显的缺点:一是加长了系统的存取周期 ,降低了整机的速度;二是 刷新过于频繁,尤其是在当存储容量比较小的情况下, 没有充分利用所允许的最大刷新间隔(2ms)

例如:对32*32的存储器,假如存储器的读写周期为0.5us,那么刷新的时间也为0.5us,则整个存储系 统周期为1us.只需32us就能对全部的存储单元刷新一遍.

图5.2-11 分散式方式示意图

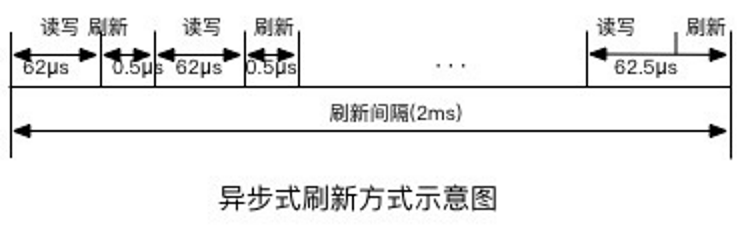

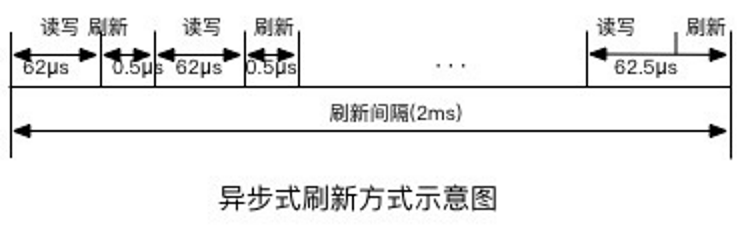

(3)异步式刷新

这种刷新方式可以看成前两种方式的结合,它充分利用了最大刷新间隔时间,把刷新操作平均 分配到整个最大刷新间隔时间内进行。

相邻两行的刷新时间=最大刷新间隔时间÷行数

对于32╳32矩阵,在2ms内需要将32行刷新一遍,所以相邻两行的刷新时间间隔 =2ms÷32=62.5μs,即每隔62.5μs安排一个刷新周期。在刷新是封锁读写。

图5.2-12 异步式方式示意图