A.5 实验五 Tomasulo算法

A.5.1 实验目的

1. 加深对指令级并行性及其开发的理解。

2. 加深对Tomasulo算法的理解。

3. 掌握Tomasulo算法在指令流出、执行、写结果各阶段对浮点操作指令以及load和store指令进行什么处理。

4. 掌握采用了Tomasulo算法的浮点处理部件的结构。

5. 掌握保留站的结构。

6. 给定被执行代码片段,对于具体某个时钟周期,能够写出保留站、指令状态表以及浮点寄存器状态表内容的变化情况。

A.5.2实验平台

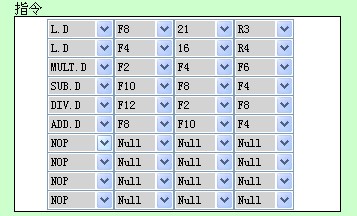

图A.5.1 “指令”区

你可以从下拉框中选择指令,供选择的指令有以下5种:

(1)L.D指令:从主存读取一个双精度浮点数;

(2)ADD.D:双精度浮点加法指令;

(3)SUB.D:双精度浮点减法指令;

(4)MULT.D:双精度浮点乘法指令;

(5)DIV.D:双精度浮点除法指令。

指令的各参数也可以从各自的下拉框中选择。

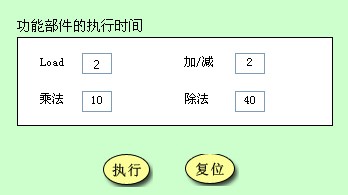

你还可以在窗口的右上区域设置各部件的执行时间(时钟周期数),如图A.5.2所示。

图A.5.2 设置功能部件时间

其中“复位”的作用是使所有设置恢复为默认值。

2. 执行

点击“执行”按钮,就进入执行状态。你可以用中间的按钮来控制指令的执行,包括“步进”、“退1步”、“前进5个周期”、“后退5个周期”、“执行到底”、“退出”等。还可以用“go”按钮直接跳转到你所指定的时钟周期。如果想修改被执行的代码,按“退出”按钮,即可回到设置指令和参数页面。

向前执行后,状态表中抹色的字段表示其内容发生了变化。

3. 对比状态表

每一个状态表的右上角外侧都有一个小三角,用鼠标左键点击它,会弹出该表在上一个时钟周期的内容。这是为了让你通过对比来了解哪些内容发生了变化。在弹出表以外的区域再次点击鼠标,就可以将其收回。

4. 各个表的内容

(1) 指令状态表

指令状态表如图A.5.3所示。它列出了各指令什么时候执行到了哪一步。其中的数字表示时钟周期,“~”表示时钟周期期间。例如,图A.5.3中的2~3表示在第2到第3个时钟周期(含第3个),第一条L.D指令是在“执行”这一步。

图A.5.3 指令状态表

其中抹色的区域表示最近一个时钟周期其内容发生了变化。下同。

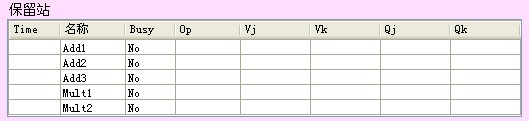

(2) 保留站

保留站的内容如图A.5.4所示。

图A.5.4 保留站

其中各字段的名称和含义如下:

Time:表示相应的保留站还有要执行多少个时钟周期;

名称:保留站的名称。用于唯一地标识相应的保留站;

Op:要对源操作数进行的操作;

Qj,Qk:将产生源操作数的保留站名称。其值等于0表示操作数已经就绪且在Vj或Vk中,或者不需要操作数。 Vj,Vk:源操作数的值。对于每一个操作数来说,V和Q字段只有一个有效。 Load部件的内容如图A.5.5所示。它按队列方式工作,每次处理新的访存都是从队列头部取走一条。

Busy:为“Yes”表示该保留站“忙”。

(3) Load部件

图A.5.5 Load部件

其中各字段的含义如下:

名称:相应单元的名称(标识);

Busy:“忙”标志,为“Yes”表示已被占用;

地址:访存的有效地址;

值:存放从存储器读来的数据。

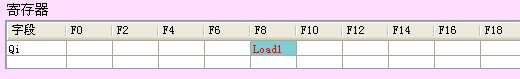

(4) 寄存器

寄存器的内容如图A.5.6所示。

图A.5.6 寄存器的内容

各字段的含义如下:

Qi:寄存器状态,用于存放将把结果写入该寄存器的保留站的站号。为0表示当前没有正在执行的指令要写入该寄存器,也即该寄存器中的内容就绪。

值:寄存器的值。

当上述表中的内容写不下时,模拟器会采用缩写的方法。这时,在上面中间的区域中会显示缩写及其值。