A.4 实验四 Cache性能分析

A.4.1 实验目的

1. 加深对Cache的基本概念、基本组织结构以及基本工作原理的理解。

2. 掌握Cache容量、相联度、块大小对Cache性能的影响。

3. 掌握降低Cache不命中率的各种方法以及这些方法对提高Cache性能的好处。

4. 理解LRU与随机法的基本思想以及它们对Cache性能的影响。

A.4.2实验平台

实验平台采用Cache模拟器MyCache。

环境的建立:见A.0。

A.4.3 实验内容及步骤

首先要掌握MyCache模拟器的使用方法(见A.4.4节)。

A.4.3.1 Cache容量对不命中率的影响

1. 启动MyCache。

2. 用鼠标点击“复位”按钮,把各参数设置为默认值。

3. 选择一个地址流文件。方法:选择“访问地址”→“地址流文件”选项,然后点击“浏览”按钮,从本模拟器所在的文件夹下的“地址流”文件夹中选取。

4. 选择不同的Cache容量,包括:2KB,4KB,8KB,16KB,32KB,64KB,128KB,256KB,分别执行模拟器(单击“执行到底”按钮即可执行),然后在表A.4.1中记录各种情况下的不命中率。

表A.4.1 不同容量下Cache的不命中率

| Cache容量(KB) | 2 | 4 | 8 | 16 | 32 | 64 | 128 | 256 |

| 不命中率 |

地址流文件名:

5. 以容量为横坐标,画出不命中率随Cache容量变化而变化的曲线。并指明地址流文件名。

6. 根据该模拟结果,你能得出什么结论?

A.4.3.2 相联度对不命中率的影响

1. 用鼠标单击“复位”按钮,把各参数设置为默认值。此时的Cache容量为64KB。

2. 选择一个地址流文件。方法:选择“访问地址”→“地址流文件”选项,然后单击“浏览”按钮,从本模拟器所在的文件夹下的“地址流”文件夹中选取。

3. 选择不同的Cache相联度,包括:直接映象,2路,4路,8路,16路,32路,分别执行模拟器(单击“执行到底”按钮即可执行),然后在表A.4.2中记录各种情况下的不命中率。

表A.4.2 当容量为64KB时,不同相联度下Cache的不命中率

| 相联度 | 1 | 2 | 4 | 8 | 16 | 32 |

| 不命中率 |

地址流文件名:

4. 把Cache的容量设置为256KB,重复(3)的工作,并填写表A.4.3。

表A.4.3 当容量为256KB时,不同相联度下Cache的不命中率

| 相联度 | 1 | 2 | 4 | 8 | 16 | 32 | |

| 不命中率 |

地址流文件名:

5. 以相联度为横坐标,画出在64KB和256KB的情况下不命中率随Cache相联度变化而变化的曲线。并指明地址流文件名。

6. 根据该模拟结果,你能得出什么结论?

A.4.3.3 Cache块大小对不命中率的影响

1. 用鼠标单击“复位”按钮,把各参数设置为默认值。

2. 选择一个地址流文件。方法:选择“访问地址”→“地址流文件”选项,然后单击“浏览”按钮,从本模拟器所在的文件夹下的“地址流”文件夹中选取。

3. 选择不同的Cache块大小,包括:16B,32B,64B,128B,256B,对于Cache的各种容量,包括:2KB,8KB,32KB,128KB,512KB,分别执行模拟器(单击“执行到底”按钮即可执行),然后在表A.4.4中记录各种情况下的不命中率。

表A.4.4 各种块大小情况下Cache的不命中率

| 块大小 (B) | Cache容量(KB) | ||||

| 2 | 8 | 32 | 128 | 512 | |

| 16 | |||||

| 32 | |||||

| 64 | |||||

| 128 | |||||

| 256 | |||||

地址流文件名:

4. 分析Cache块大小对不命中率的影响。

A.4.3.4 替换算法对不命中率的影响

1. 用鼠标单击“复位”按钮,把各参数设置为默认值。

2. 选择一个地址流文件。方法:选择“访问地址”→“地址流文件”选项,然后单击“浏览”按钮,从本模拟器所在的文件夹下的“地址流”文件夹中选取。

3. 对于不同的替换算法、Cache容量和相联度,分别执行模拟器(单击“执行到底”按钮即可执行),然后在表A.4.5中记录各种情况下的不命中率。

表A.4.5 LRU和随机替换法的不命中率的比较

| Cache 容量 | 相 联 度 | |||||

| 2 路 | 4 路 | 8 路 | ||||

| LRU | 随机算法 | LRU | 随机算法 | LRU | 随机算法 | |

| 16KB | ||||||

| 64KB | ||||||

| 256KB | ||||||

| 1MB | ||||||

地址流文件名:

4. 分析不同的替换算法对Cache不命中率的影响。

A.4.4 MyCache模拟器使用方法

1. 启动模拟器:用鼠标双击MyCache.exe。

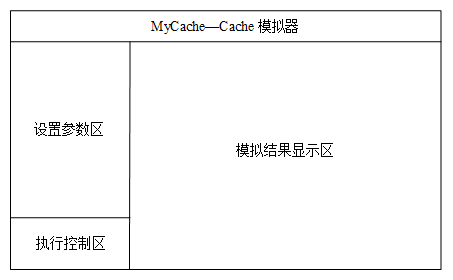

2. 系统会打开一个操作界面。该界面的左边为设置模拟参数区域,右边为模拟结果显示区域。如图A.4.1所示。

3. 可以设置的参数包括:是统一Cache还是分离Cache,Cache的容量,块大小,相联度,替换算法,预取策略,写策略,写不命中时的调块策略。可以直接从列表里选择。

4. 访问地址可以选择来自地址流文件,也可以选择手动输入。如果是前者,则可以通过点击“浏览”按钮,从模拟器所在文件夹下面的“地址流”文件夹中选取地址流文件(.din文件),然后进行执行。执行的方式可以是步进,也可以是一次执行到底。如果选择手动输入,就可以在“执行控制”区域中输入块地址,然后点击“访问”按钮。系统会在界面的右边显示访问类型、地址、块号以及块内地址。

5. 模拟结果包括:

(1)访问总次数,总的不命中次数,总的不命中率;

(2)读指令操作的次数,其不命中次数及其不命中率;

(3)读数据操作的次数,其不命中次数及其不命中率;

(4)写数据操作的次数,其不命中次数及其不命中率;

(5)手动输入单次访问的相关信息。

图A.4.1 MyCache模拟器的操作界面示意图