数字钟的电路设计

上一节

下一节

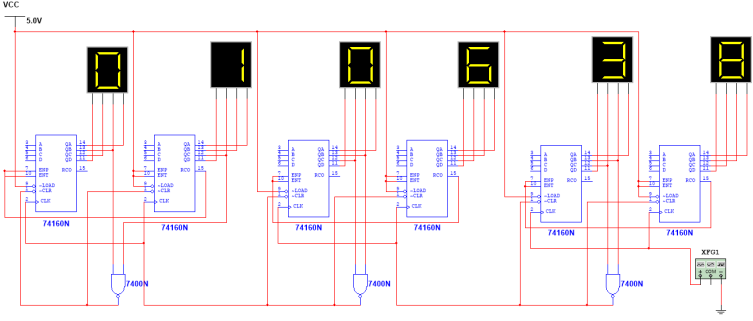

设计思路:数字钟选用6片十进制计数器74LS160实现,秒和分连接为60进制计数器,小时连接为24进制计数器,用6个数码管显示时分秒六位数。秒脉冲采用函数发生器产生1Hz方波,秒计数器和分计数器按照反馈清零法接成60进制计数器,时计数器按照反馈清零法接成24进制计数器,秒计数器清零端连接分计数器的时钟脉冲端,当秒计数器逢59进1的时候,产生的进位信号为分计数器产生时钟下降沿,分计数器加1。同理,分计数器清零端连接时计数器的时钟脉冲端,当分计数器逢59进1的时候,产生的进位信号为时计数器产生时钟下降沿,分计数器加1。以上就是简易数字钟的设计思路。

仿真电路如图7.33所示。点运行,可以看到数码管开始计数,为了方便测试,可以增大秒脉冲频率,观察秒向分进位、分向时进位是否正确,观察当数字钟运行到23时59分59秒时,下一个状态系统是否清零,重新开始计数。

图7.33 简易数字钟测试电路