一、由JK触发器构成的异步十六进制加法计数器功能测试

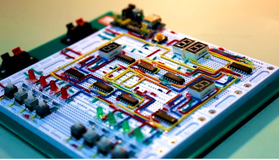

打开Multisim软件,放置4个JK触发器 74LS76,时钟端接信号源,设计波形为矩形波,占空比50%,频率10Hz,振幅5V,将四个触发器的输出接2.5V指示灯,用来显示输出状态,将J、K接高电平1,根据触发器功能可知,触发器出于翻转状态,前一个触发器的输出Q做为下一个触发器的时钟脉冲源,当前一个触发器从高电平向低电平跳变的时候,下一个触发器翻转,从而实现了加法计数。测试电路如图7.27所示。打开逻辑分析仪面板,可以观察波形。

改变电路连线,将前一个触发器的做为下一个触发器的时钟脉冲,可以实现减法计数,读者自行分析。

图7.27 JK触发器构成的异步十六进制加法计数器测试

二、双向移位寄存器功能测试

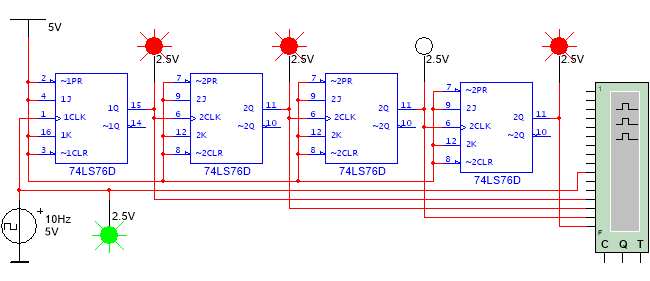

打开Multisim软件,放置4位双向移位寄存器 74LS194,时钟端接信号源,设计波形为矩形波,占空比50%,频率1Hz,振幅5V,将移位寄存器输出接2.5V指示灯,用来显示数据移动状态,将并行数据输入端ABCD接四路逻辑开关,通过开关通断表示二进制0和1,将工作方式控制端S1和S0接两路逻辑开关,右移串行数码输入端SR和左移串行数码输入端SL接两路逻辑开关,将清零端CLR接三脚拨动开关,被测电路如图7.28所示。

运行电路,功能测试如下:

1.异步清0。只要给复位(清0)端CLR加低电平,寄存器就清0,Q3 Q2 Q1 Q0=0000。

2.右移移位。当CLR=1、工作方式控制端S1S0=01时,在时钟脉冲CLK上升沿作用下,右移数据SR存入寄存器并右移。

3.左移移位。当CLR=1、工作方式控制端S1S0=10时,在时钟脉冲CLK上升沿作用下,左移数据SL存入寄存器并左移。

4.并行置数。当CLR=1、工作方式控制端S1S0=11时,在时钟脉冲CLK上升沿作用下,DC B A输入的数码并行送入寄存器,QD QC QB QA=DC B A。

5.保持功能。当CLR=1、工作方式控制端S1S0=00时,或者CLR=1、CLK=0时,移位寄存器处于保持功能。

图7.28 双向移位寄存器 74LS194功能测试

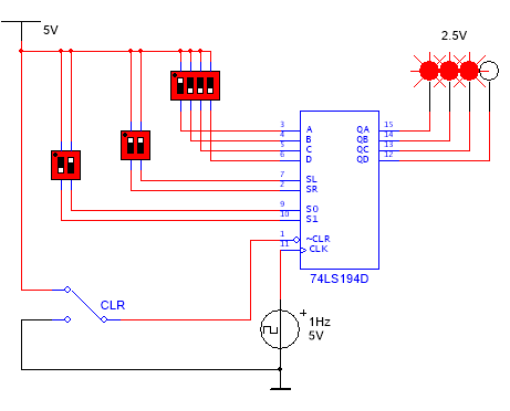

用双向移位寄存器 74LS194可构成循环灯电路,右移数据输入高电平1,右移时从左至右依次点亮四个灯,左移数据输入低电平0,左移时从右到左依次灭掉四个灯,电路通过下降沿JK触发器的两个互补输出端控制移位寄存器工作方式控制端S1S0,实现往返自动切换。

将74LS73的JK端接高电平,使触发器出于翻转功能,将74LS73两个互补输出端接到74LS194的工作模式控制端S₁S₀上,S1S0=01时右移,S1S0=10时左移。当高电平1右移至QD 时,产生下降沿的触发脉冲,JK触发器翻转,由右移模式变为左移模式;当低电平0左移至QA时,产生下降沿的触发脉冲,JK触发器再次翻转,又由左移模式变为右移模式,以此类推,循环往复。

设计思路如下:将QA和QD连接异或门输入端,将异或门输出连接触发器的时钟脉冲端,在4个指示灯全部点亮前,74LS194工作于右移模式,此时QA和QD相异为1,,当4个指示灯全部点亮时,QA和QD相同为0,,此时异或门的输出由1变为0,产生下降沿脉冲信号,触发器输出翻转,切换至左移状态。同理左移时,4个指示灯全部熄灭前,QA和QD相异为1,,当4个指示灯全部熄灭时,QA和QD相同为0,,此时异或门的输出再次由1变为0,产生下降沿脉冲信号,触发器输出翻转,移位寄存器切换至右移状态。测试电路如图7.29所示。

图7.29 双向移位寄存器 74LS194构成的循环灯测试

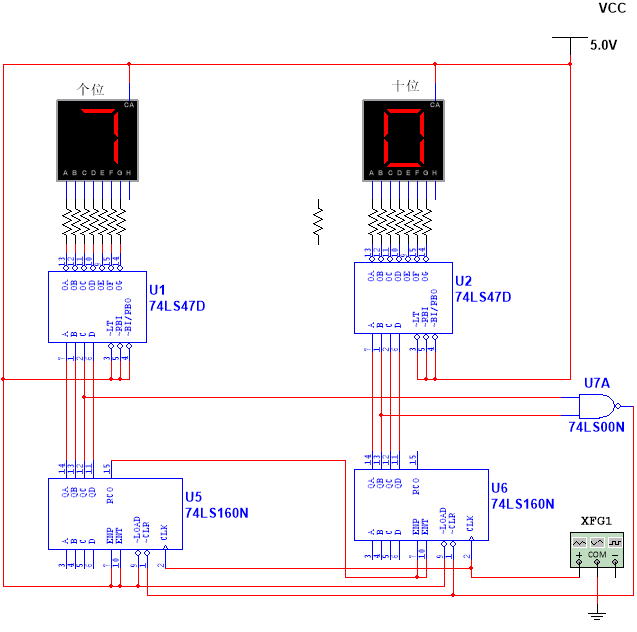

三、24进制计数器功能测试

1.异步清零法实现24进制计数器

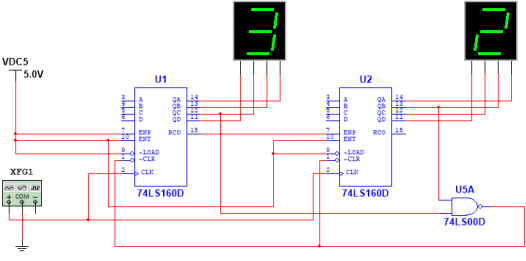

打开Multisim软件,放置两个十进制计数器 74LS160,将低位片(个位)的进位输出端连接高位片(十位)的计数控制端ENP和ENT,低位逢10进位时,高位计数1次,实现逢10进1功能。74LS160为异步清零方式,采用反馈清零法,当计数到24时,将中间状态24转换为清零信号,计数器将重新开始计数。24对应的8421BCD码为00100100,将高电平对应的两个输出端连接与非门的输入端,将与非门输出的0信号连接清零端CLR,每当计数到24时计数器立刻清零,实现了24进制计数功能。测试电路如图如图7.30所示。

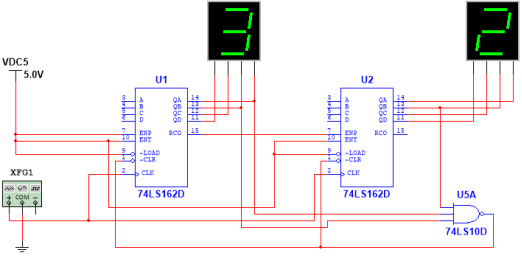

2.同步清零法实现24进制计数器

将计数器替换为74LS162,观察实验现象,发现74LS162清零方式为同步清零,即清零端获得清零信号后,没有立刻清零,而是要等待下一个计数脉冲到来时才清零,因此采用74LS162实现24进制计数器时,反馈的中间状态为23。23对应的8421BCD码为00100011,将高电平对应的三个输出端连接与非门的输入端,将与非门输出的0信号连接清零端CLR,每当计数到23时,清零端获得清零信号,等待下一个脉冲到来时,计数器清零,回到初始状态,实现了24进制计数功能。测试电路如图如图7.31所示。

图7.30 异步清零法构成24进制计数器

图7.31 同步清零法构成24进制计数器

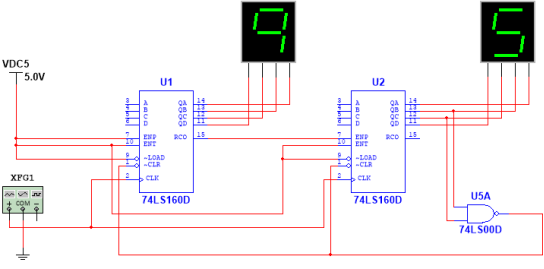

四、60进制计数器功能测试

分别利用十进制计数器74LS160、74LS162实现60进制计数器,方法和24进制计数器一样,读者自行分析。测试电路如图如图7.32所示。

思考:如果采用16进制计数器,又该如何实现呢?

图7.32 异步清零法构成60进制计数器