一、Multisim逻辑分析仪

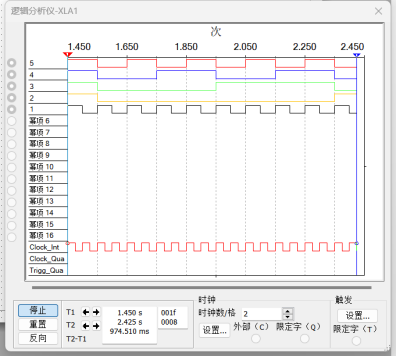

逻辑分析仪(Logic Analyzer) 可以同步记录和显示16位数字信号,可用于对数字信号 的高速采集和时序分析,逻辑分析仪的图标、显示界面、设置界面如图7.22所示。

图7.22 逻辑分析仪显示界面

逻辑分析仪左侧从上到下有16个接线端子,用于接入被测信号。底部有3个接线端子, C 是外部时钟输入端,Q是时钟控制输入端,T是触发控制输入端。

逻辑分析仪的操作面板分为图形显示区、显示控制区、游标测量数据显示区、Clock 控制区、Trigger控制区。

1. 图形显示区:面板最左侧16个小圆圈代表16个输入端,如果某个连接端接有被测信号,则该小圆圈内出现一个黑圆点。被采集的16路输入信号依次显示在屏幕上。当改变 输入信号连接导线的颜色时,显示波形的颜色立即相应改变。

2. 显示控制区:用于控制波形的显示与清除。有3个按钮,其功能如下:

停止(Stop )按钮:停止逻辑分析仪的波形继续显示。

重置(Reset) 按钮:逻辑分析仪复位并清除显示波形。

反向(Reverse)按钮:改变屏幕背景的颜色。

3. 游标测量数据显示区:移动游标上部的三角形可以读取波形的逻辑数据。T1 和 T2 分别表示游标1和游标2离开扫描线零点的时间,T2-T1 表示两者之间的时间差。

4. 时钟(Clock)控制区:包括时钟数/格(Clock/Div)编辑框及设置(Set)按钮。

钟数/格(Clock/Div): 显示屏上每个水平刻度显示的时钟脉冲数。

设置(Set)按钮:设置时钟脉冲,单击该按钮,弹出时钟设置(Clock Setup)对话框。时钟源(Clock source)分外部(External)和内部(Internal),通常选内部;时钟频率(Clock rate)编辑区域是设置时钟频率,应和被测信号频率数量级保持一致;采样设置(Sampling setting)包括预触发样本(Pre-trigger samples)、后触发样本(Post-trigger samples)和阈值电压(Threshold Volt)设置。

二、用逻辑分析仪测试计数器功能

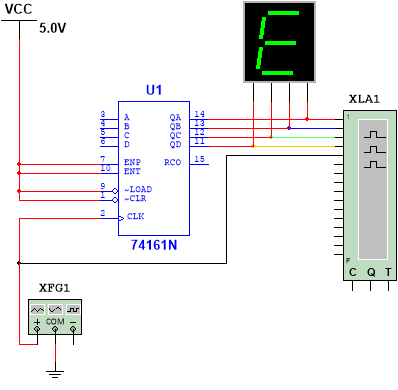

打开Multisim软件,放置十六进制计数器 74LS161,时钟端接函数发生器,设计波形为矩形波,占空比50%,频率10Hz,振幅8V,将计数器输出接十六进制数码管,用来显示计数状态,放置逻辑分析仪,将四路输出和时钟源分别接入,用不同颜色的线加以区分,被测电路如图7.23所示。

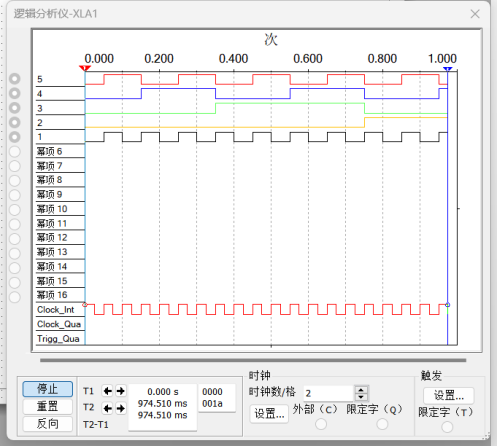

将逻辑分析仪“时钟数/格”设置为2,点设置将时钟频率设置为20Hz,运行电路,得到波形图如图7.24所示,可以看出,输出从低位到高位频率依次减半,逻辑分析仪测得的时序波形完全符合计数器74LS161逻辑功能。

用同样的方法测试计数器 74LS160、74LS162、74LS163,总结它们的功能有什么异同。

图7.23 计数器74LS161测试电路

图7.24 逻辑分析仪显示界面