一、JK触发器功能仿真测试

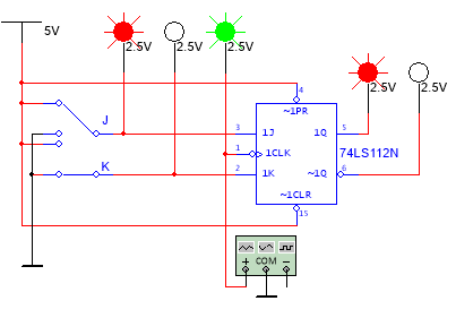

将JK触发器的J、K触发端接三脚开关,直接置0(复位)端和直接置1(置位)端接高电平,时钟端接入函数发生器,设置波形为方波,频率为1HZ,1HZ的目的是为了方便观察灯的闪烁,设置界面如图5.9所示。仿真电路如图5.10所示。

功能验证:

拨动开关,令J=1,K=0,J端对应的灯亮,K端对应的灯不亮,触发器出于置1功能,输出Q端灯亮;

拨动开关,令J=1,K=1,触发器出于翻转功能,输出Q端和端交替闪烁;

拨动开关,令J=0,K=1,触发器出于置0功能,输出端灯亮;

拨动开关,令J=0,K=0,触发器出于保持功能,输出保持不变。

图5.10 JK触发器74LS112功能仿真测试

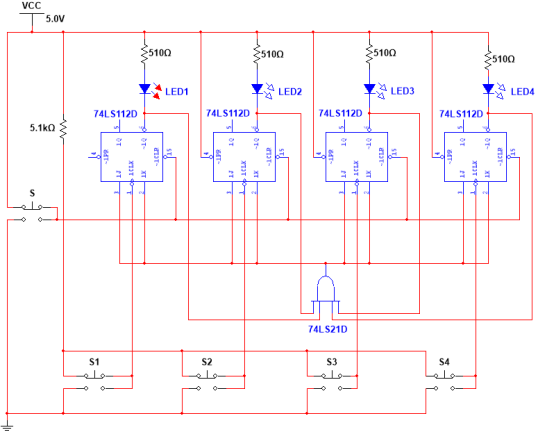

二、 4路抢答电路设计

本项目要求利用边沿JK触发器和逻辑门,设计制作一个4路抢答器,第一个按下抢答按钮者,其相应的发光二极管发光,表示此人抢答成功;而紧随其后的其他开关再被按下均无效;要求电路具有复原功能,电路复原后可以进行下一轮抢答。

设计思路:

可选择下降沿触发的JK触发器,将抢答按钮与脉冲端相连,按钮不按的时候与电源正极相连,为高电平1,按下抢答按钮,切换至低电平0,于是脉冲端产生一个下降沿,松开按钮,回到高电平状态。

由于初始状态,要先进行清零,输出Q=0,,此时灯都不亮,因此发光二极管需要接在和电源之间,第一个按下抢答按钮的触发器由于先得到了脉冲下降沿,发生动作,输出状态从初始1变为0,点亮发光二极管,因此要求初始状态触发器的J、K都是高电平,高电平触发信号可由4输入与门实现,方法是将四个抢答器的做为与门的输入。当第一个按下抢答按钮的触发器从初始1变为0,与门的输出也变成了0,其余触发器出于保持状态,紧随其后的其他开关再被按下均无效。清零按钮和触发器的直接置0端相连。

将设计思路在Multisim软件中进行仿真测试,测试电路如图5.11所示。

测试过程:运行电路,按下清零按钮,四个发光二极管都不亮。随意按下一个抢答按钮,对应触发器输出端的发光二极管亮,再按下其余按钮,对应的灯都不亮。功能验证达到正常。

图5.11 JK触发器构成的4路抢答器仿真测试