加法显示电路设计

本项目要求利用集成加法器、数码管设计制作加法显示电路,电路启动之后,可进行二进制加法运算,并把计算结果显示在数码管上。

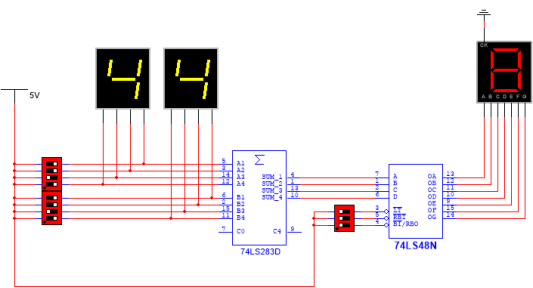

一、十进制加法电路设计

电路如图4.22所示,这种方法可以显示9以内的加法,当加法结果大于9,数码管将显示乱码。如图所示,二进制十进制0100+0100=1000,即4+4=8,结果显示8。

图4.22 十进制加法显示电路

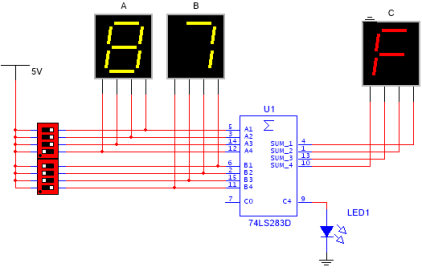

二、4位二进制(十六进制)加法电路设计

采用十六进制数码管显示计算结果时不需要译码器驱动,电路更简洁,可显示15以内的运算结果,当结果大于9时显示字母A到F,当结果大于15时,9号引脚进位端C4连接的发光二极管亮。如图4.23所示,1000+0111=1111,即7+8=15,数码管显,15对应的十六进制数F,此时没有进位,进位端输出低电平0,发光二极管不亮。当结果大于15时,需要进行修正,才能显示对应的8421BCD码。

图4.23 二进制加法显示电路测试

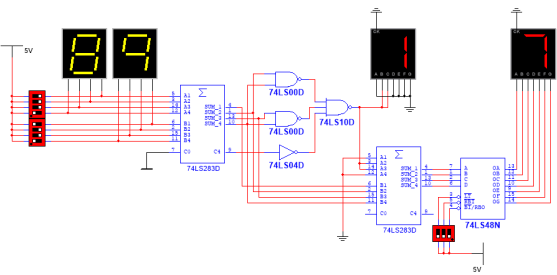

三、二—十进制加法显示电路设计

1位十进制数由4位二进制BCD码组成,由于两个4位二进制数加法“逢十六进一”,而十进制数则是“逢十进一”,这样就造成十进制数运算和8421码运算时,在进位时差6,

当0100+0011=0111时,,一位数码管显示没问题,而0110+1000=1110时,即6+8=14时,此时和大于9,超出了一位数码管显示范围,就需两个数码管表示,一个显示十位数1,一个显示个位数4。个位的4需要将14进行减10修正,而减去10相当于加上6,因此当和的结果大于9时,需要加6修正后用来表示个位数。

当和大于9小于16时,进位端C4输出0,并没有产生进位信号,十位数的1该如何表示呢?从表4-9可以看出此时S4S3同时为1,或者S4S2同时为1,即可以将S4S3+S4S2=1做十位数的条件。当和大于15时,进位端C4输出的高电平1,因此,十位数的1由C4+S4S3+S4S2产生,将式子变换成与非门形式,即。

表4-8 8421BCD码加法电路真值表

进位端C4 | S4 | S3 | S2 | S1 | 对应十进制数 | 十位BCD码 | 个位BCD码 |

0 | 1 | 0 | 0 | 1 | 9 | 0000 | 1001 |

0 | 1 | 0 | 1 | 0 | 10 | 0001 | 0000 |

0 | 1 | 0 | 1 | 1 | 11 | 0001 | 0001 |

0 | 1 | 1 | 0 | 0 | 12 | 0001 | 0010 |

0 | 1 | 1 | 0 | 1 | 13 | 0001 | 0011 |

0 | 1 | 1 | 1 | 0 | 14 | 0001 | 0100 |

0 | 1 | 1 | 1 | 1 | 15 | 0001 | 0101 |

1 | 0 | 0 | 0 | 0 | 16 | 0001 | 0110 |

1 | 0 | 0 | 0 | 1 | 17 | 0001 | 0111 |

1 | 0 | 0 | 1 | 0 | 18 | 0001 | 1000 |

1 | 0 | 0 | 1 | 1 | 19 | 0001 | 1001 |

综上所述,电路需要三个部分:一是4位加法器完成两个数相加;一是判别电路,决定是否修正;三是加6修正电路。其中第一和第三均为加法,可由4位全加器实现。第二部分判别电路由与非门组成,实现电路如图4.24所示,图中1000+1001=10001,产生进位信号1,经过修正后显示00010111,即十进制17。

当电路大于19时,又该如何显示?请读者自行完成。

图4.24 二-十进制加法显示电路