三变量多数表决电路仿真设计

上一节

下一节

下面通过 Multisiml4中用虚拟逻辑变换器完成三变量多数表决电路的设计与测试。

一、电路设计

1.双击逻辑转换仪打开其面板。

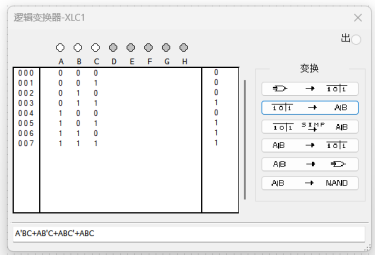

2.在逻辑分析仪的输入端单击A、B、C, 真值表区将三个输入变量的所有组合形式列 出来,在输出列单击每一个输出,选择与输入取值组合及相应的输出,点击右侧第二个图标按钮,在下方逻辑表达式栏可以看到逻辑表达式。如图2.18所示。

图2.18 “真值表→逻辑表达式”的转换

3.得到最简表达式

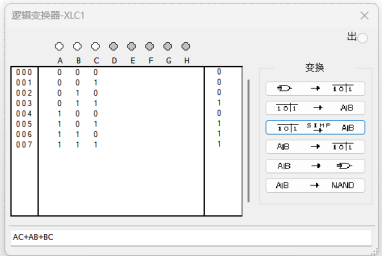

点击右侧第三个图标按钮,可得到最简表达式,如图2.19所示。

图2.19 “真值表→最简逻辑表达式”的转换

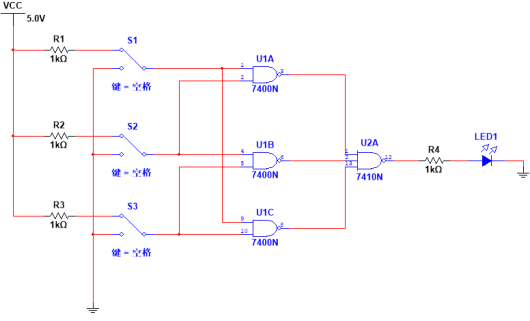

4.得到与非门组成的逻辑电路图

点击右侧第六个图标按钮,最简表达式变换成与非门的形式,可得到由与非门组成的逻辑电路图,逻辑变换器自动选择2输入与非门来完成,我们将电路修改成由2输入与非门和3输入与非门的电路形式,如图2.20所示。

图2.20 与非门组成的三人表决器电路图

二、电路仿真

将三个输入端连接拨动开关,开关置于电源正极,为高电平1,表示同意;开关置于地,为低电平0,表示不同意。将输出端连接发光二极管做为指示灯,指示灯亮为决议通过,不亮为不通过。依次测试真值表的八个组合,测试电路功能是否和真值表一致。如图2.20所示。

可见,利用逻辑转换仪来做组合逻辑电路的设计,省去了公式化简,提高了效率,同时也提高了设计的正确性。