课后作业

1.选择题

(1)在VHDL语言中,下列对时钟边沿检测描述中,错误的是( )。

A.ifclkeventand clk=‘1’then B.iffalling_edge(clk)then

C.ifclkeventand clk=‘0’then D.ifclkstableand not clk=‘1’then

(2)不完整的IF语句,其综合结果可实现( )。

A.时序逻辑电路B.组合逻辑电路

C.双向电路 D.三态控制电路

(3)STD_LOGIG_1164中定义的高阻是字符( )。

A.X B.x C.z D.Z

(4)转换函数TO_BITVECTOR()的功能( )。

A.将STDLOGIC_VECTOR转换为BIT_VECTOR

B.将REAL转换为BIT_VECTOR

C.将TIME转换为BIT_VECTOR

D.以上说法都错误

2.填空题

(1)端口a为8位二进制双向端口,则应用VHDL语言,端口的定义可表示为( )。当端口a作为输入端口时,需将端口a的输出状态( ) 。

(2)b为整数类型对象,c为3位标准逻辑对象,利用转换函数将b的值赋给c,VHDL语句表达为( ) 。使用转换函数前,首先要对( )库中的程序包( )进行声明。

(3)同步置/复位是( ) ;异步置/复位是( ) 。如果采用异步复位方式,时钟信号clk上升沿有效,复位信号rst低电平有效,则以下程序可表示为:

IF( ) THEN

…

ELSIF( ) THEN

…

ENDIF;

(4)VHDL预定义的’+’运算符只用于( )类型的对象,如果要对其他类型的对象进行加法操作,则可以对运算符进行重新定义,这个过程称为( ) ,通过这种方式实现标准逻辑类型对象的加法操作,需首先对( ) 库的( )程序包进行声明。

3.编程题

(1)请设计一个四选一多路选择器,端口宽度为16位。

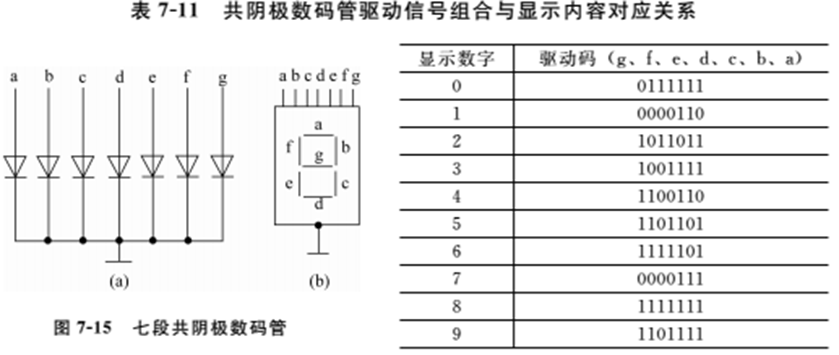

(2)七段数码管由七个发光二极管组成,通过七个发光二极管亮暗的不同组合,可以显示多种数字、字母以及其他符号。要使数码管显示正确的内容,必须根据要显示的内容向数码管送出驱动信号,即进行译码驱动。以共阴极数码管为例,显示内容和驱动信号组合对应关系如表所示。请编写程序,驱动共阴极数码管显示不同内容。

(3)请设计一个8位移位寄存器,对寄存器中的数据进行逻辑左移或逻辑右移,datain为需移位的8位数据输入,q为移位后的8位数据输出,clk为时钟脉冲输入,每个时钟脉冲到来数据移动一位;dir为方向控制,dir=‘1’时对数据进行左移,dir=‘0’时对数据进行右移。

(4)设计一个减法计数器,计数初值通过datain端口输入,外部脉冲通过cp输入,当计数值为0时,外部脉冲输入后计数值恢复为初值,同时进位输出端co输出进位脉冲。