任务7.2 常用时序逻辑电路的设计

7.2.1触发器的设计

【提示】触发器(FlipFlop)是一种可以存储电路状态的存储单元,在实际的数字系统中而且经常要求存储单元在同一时刻同步动作,为达到这个目的,在每个存储单元电路上引入一个时钟脉冲(CLK)作为控制信号,只有当CLK到来时电路才被“触发”而动作,并根据输入信号改变输出状态。我们把这种在时钟信号触发时才能动作的存储单元电路称为触发器。

典型触发器包括RS触发器、D触发器、JK触发器、T触发器,典型数字电路芯片有7474(D触发器)、7473(JK触发器)、7476(JK触发器)等。

触发器可增加使能功能、异步置/复位功能和同步置/复位功能,这些功能都可利用VHDL语言实现。

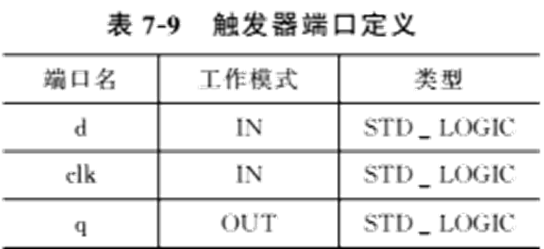

任务:设计一个一位D触发器。

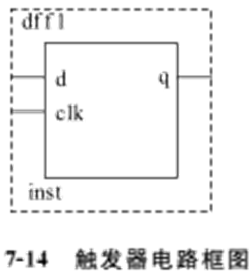

简单D触发器的电路框图如图7-14所示。根据电路框图,端口定义为:

根据端口定义,实体可描述为:

LIBRARYIEEE;USE IEEE.STD_LOGIC_1164.ALL;

ENTITYdff1 IS

PORT(d:INSTD_LOGIC;clk:INSTD_LOGIC;

q:OUTSTD_LOGIC);END dff1;

根据D触发器的作用,在时钟clk有效时,将输入信号d赋值到输出信号q,采用行为描述方式,结构体可表示为:

ARCHITECTUREbehavOF dff1 IS

BEGIN

PROCESS(a)

IF(时钟有效)THEN

y<=a;ENDIF;END PROCESS;END beahv;

时钟触发方式有电平触发和边沿触发两种。电平触发可表示为:

IFclk=‘1’THEN ——高电平触发

IFclk=‘0’THEN ——低电平触发

或

IF(clk’STABLEAND clk=‘1’)THEN ——高电平触发

IF(clk’STABLEAND clk=‘0’)THEN ——低电平触发

其中STABLE为信号属性,当信号没有发生变化时,STABLE属性的值为真(true);当信号在采样时间内发生了变化时,STABLE属性的值为假(false)。

边沿触发可表示为:

IF(clk’EVENTAND clk=‘1’)THEN ——上升沿触发

IF(NOT clk’STABLEAND clk=‘1’)THEN ——上升沿触发

IF(clk’EVENTAND clk=‘0’)THEN ——下降沿触发

IF(NOT clk’STABLEAND clk=‘0’)THEN ——下降沿触发

其中EVENT为信号属性,当信号在采样时间内发生变化时,EVENT属性的值为真(true);当信号在采样时间内没有发生变化时,EVENT属性的值为假(false),与STABLE相反。clkEVENT相当于NOTclkSTABLE

边沿触发还可采用LAST_VALUE属性进行描述:

IFclk=‘1’AND clk’LAST_VALUE=‘0’THEN ——上升沿触发

IFclk=‘0’AND clk’LAST_VALUE=‘1’THEN ——下降沿触发

LAST_VALUE属性为信号跳变前的值。

边沿触发还可利用函数进行判断:

IFRISING_EDGE(clk)THEN ——上升沿触发

IFFALLING_EDGE(clk)THEN ——下降沿触发

可用rising_edge()函数检测信号是否有上升沿变化,若有则条件为真。falling_edge()函数检测信号是否有下降沿变化,若有则条件为真。只有标准逻辑类型的信号(STD_LOGIC)可使用边沿检测函数。

【例7-13】

LIBRARYIEEE;USE IEEE.STD_LOGIC_1164.ALL;

ENTITYdff1 IS

PORT(d:INSTD_LOGIC;clk:INSTD_LOGIC;

q:OUTSTD_LOGIC);END dff1;

ARCHITECTUREbehavOF dff1 IS

BEGIN

PROCESS(clk,d)

BEGIN

IF(clk’EVENTAND clk=‘1’)THEN

q<=d;ENDIF;END PROCESS;END behav;

触发器可加上复位信号、置位信号和使能信号,其中复位、置位可分为同步方式和异步方式。同步方指是指在置/复位和时钟信号同时有效时,时序电路才被置/复位;异步方式是指当置/复位有效时,时序电路立即被置位或复位,与时钟信号无关。

复位信号为rst,在D触发器上添加异步复位方式,可表示为:

IFrst=‘1’THEN

q<=‘0’;

ELSIF(clk’EVENTAND clk=‘1’)THEN

q<=d;ENDIF;

置位信号为set,在D触发器上添加同步置位方式,可表示为:

IF(clk’EVENTAND clk=‘1’)’THEN

IFset=‘1’ THEN

q<=‘1’;

ENDIF;

ELSE

q<=d;

ENDIF;

【例7-14】

LIBRARYIEEE;USE.IEEE.STD_LOGIC_1164.ALL;

ENTITYdff2 IS

PORT(d:INSTD_LOGIC;rst,set:INSTD_LOGIC;

en:INSTD_LOGIC;clk:INSTD_LOGIC;

q:OUTSTD_LOGIC);END dff2;

ARCHITECTUREbehavOF dff2 IS

BEGIN

PROCESS(clk,d, en,rst,set)

BEGIN

IFen=‘1’THEN

IFrst=‘1’THEN

q<=‘0’;

ELSIFset=‘1’ THEN

q<=‘1’;

ELSE

IF(clk’EVENTAND clk=‘1’)THEN

q<=d;

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;END behav;

7.2.2计数器的设计

【提示】计数器是常用的数字电路元件,基本功能是对输入的时钟脉冲进行计数。常用的计数器芯片有74161(同步二进制计数器)、74160(同步十进制计数器)、74192(十进制可逆计数器)、74LS90(异步计数器)等。

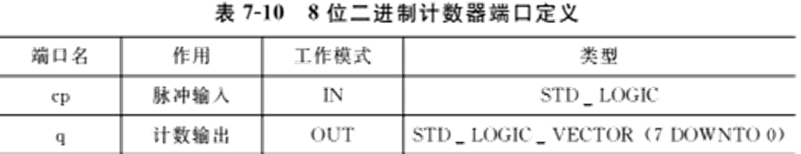

任务1.设计一个8位二进制加法计数器。电路框图如图7-15所示

在电路框图中,端口定义为:

因此实体可表述为:

LIBRARYIEEE;USE IEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYcounter8 IS

PORT(cp:IN STD_LOGIC;

q: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

ENDcounter8;

采用行为描述方式,结构体可表述为:

ARCHITECUREbehavOF counter8 IS

BEGIN

PROCESS(clk)

VARIABLEq1: STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

IF(cp’EVENTAND cp=‘1’)THEN

q1:=q1+1;

ENDIF;

ENDPROCESS;

ENDbehav;

【例7-15】

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYcounter8 IS

PORT(cp:IN STD_LOGIC;

q:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

ENDcounter8;

ARCHITECTUREbehavOF counter8 IS

BEGIN

PROCESS(cp)

VARIABLEq1: STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

IF(cp’EVENTAND cp=‘1’)THEN

q1:=q1+1;

ENDIF;

q<=q1;

ENDPROCES;

ENDbehav;

任务2.设计一个二十进制计数器

设计一个二十进制计数器,计数器具有使能、异步置/复位、进位输出功能。

【例7-16】

LIBRARYIEEE;USE IEEE.STD_LOGIC_1164.ALL;

ENTITYcounter20 IS

PORT(cp:IN STD_LOGIC;

en:IN STD_LOGIC; ——使能端

set,reset:IN STD_LOGIC; ——置位/复位端

datain:IN INTEGER RANGE 0 TO 19; ——置位初值输入

co:OUT STD_LOGIC; ——进位输出

q:BUFFER INTEGER RANGE 0 TO 19); ENDcounter20;

ARCHITECTUREbehavOF counter20 IS

BEGIN

PROCESS(cp)

BEGIN

IFen=‘1’THEN

Ifreset=‘1’ THEN

q<=0;

ELSIFset=‘1’ THEN

q<=datain;

ELSE

IF(cp’EVENTAND cp=‘1’)THEN

IFq<19 THEN

q<=q+1;

co<=‘0’;

ELSE

q<=0;

co<=‘1’;

ENDIF;

ENDIF;

ENDIF;

ENDIF;END PROCESS;END behav;