课后作业

1.基础题

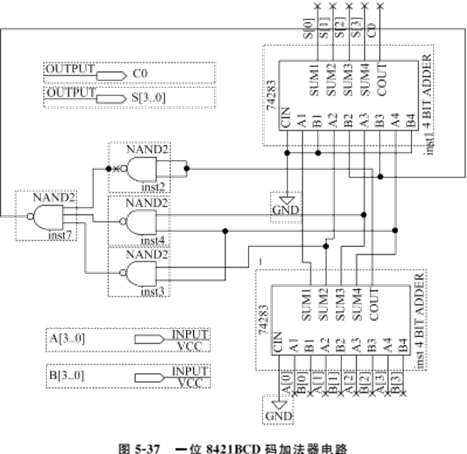

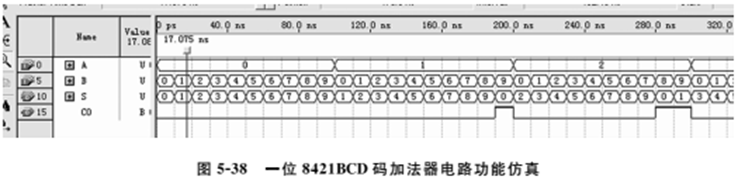

用74283加法器和逻辑门设计实现一位8421BCD码加法器电路,输入输出均为BCD码,Ci为低位的进位信号,Co为高位的进位信号,输入为两个1位十进制数A和B,输出用S表示。原理图及功能仿真波形如图5-37和图5-38所示。

2.实训题

用74390和74374设计两位十进制频率计,tf_ctro子模块原理图和顶层文件原理图如下图5-39和图5-40所示。将各个子模块编译后仿真验证功能,然后将顶层设计文件分配管脚后下载至开发板。

显示模块程序:

libraryieee;

useieeestd_logic_1164all;

useieeestd_logic_unsignedall;

entitydecl7s2 is

port(clk∶instd_logic;

data1,data2∶instd_logic_vector(3downto0);

dip∶outstd_logic_vector(1downto0);

led∶outstd_logic_vector(6downto0));

enddecl7s2;

architecturebehave of decl7s2 is

signaldata∶std_logic_vector(3downto0);

signalcnt∶std_logic_vector(24downto0);

begin

process(clk)

begin

if(clk=‘1’andclkevent)then

cnt<=cnt+1;

endif;

endprocess;

process(cnt(18))

begin

casecnt(18)is

when‘0’=>data<=data1;dip<=“10”;

when‘1’=>data<=data2;dip<=“01”;

whenothers=>null;

endcase;

casedata is

when“0000”=>led<=“0000001”;

when“0001”=>led<=“1001111”;

when“0010”=>led<=“0010010”;

when“0011”=>led<=“0000110”;

when“0100”=>led<=“1001100”;

when“0101”=>led<=“0100100”;

when“0110”=>led<=“0100000”;

when“0111”=>led<=“0001111”;

when“1000”=>led<=“0000000”;

when“1001”=>led<=“0000100”;

when“1010”=>led<=“0001000”;

when“1011”=>led<=“1100000”;

when“1100”=>led<=“0110001”;

when“1101”=>led<=“1000010”;

when“1110”=>led<=“0110000”;

when“1111”=>led<=“0111000”;

whenothers=>null;

endcase;

endprocess;

endbehave;