任务8.2 综合设计应用

上一节

任务8.2 综合设计应用

8.2.1数字钟的设计

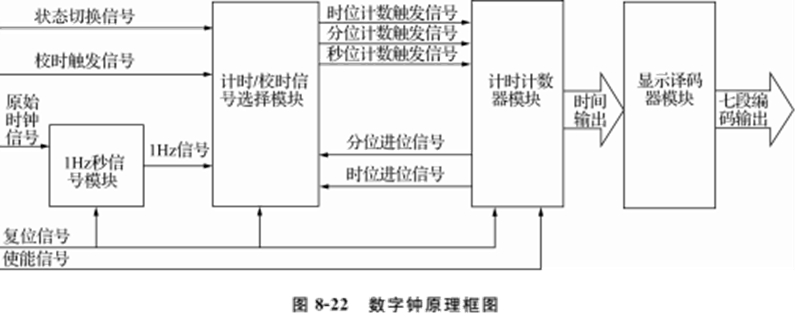

用VHDL语言编写程序实现数字钟的端口控制信号如图8-21所示。

1.cp信号是外部时钟信号,对该信号进行分频后得到1Hz的秒信号。

2.rst是数字钟的全局复位信号。

3.en为使能控制信号。

4.state为计时、校时、校分、校秒功能切换信号。

5.ch_bt为手动校时触发信号。

6.led_h1、led_h0、led_m1、led_m0、led_s1、led_s0分别为数字钟时位、分位、秒位的十位与个位的七段编码输出信号。

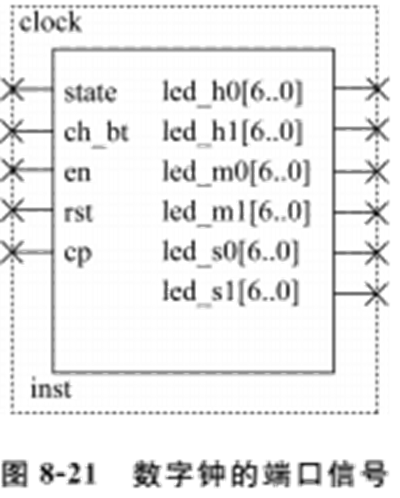

用VHDL语言编写程序实现数字钟功能,其原理框图如图8-22所示,由4个模块构成。

具体运行方式如下:

校时状态,时位计数触发信号端口输出校时触发信号,分位和秒位计数触发信号端口输出低电平信号。

校分状态,分位计数触发信号端口输出校时触发信号,时位和秒位计数触发信号端口输出低电平信号。

校秒状态,秒位计数触发信号端口输出校时触发信号,时位和分位计数触发信号端口输出低电平信号。

计时计数器模块包括一个24进制计数器和两个60进制计数器,三个计数器相互独立,由前级的计时/校时信号选择模块分别对它们提供触发信号。而秒位和分位的两个60进制计数器需要输出两个进位信号,反馈回前级,以便分位和时位正常完成计数功能。