项目8 硬件描述语言的设计应用

近些年,随着电子技术及计算机技术的不断发展, VHDL语言被越来越广泛地应用到电子设计自动化中,显著地提高了开发效率及产品的可靠性。

VHDL语言可以理解成一种快捷的电路设计工具,其功能主要包括电路合成、 电路描述及电路仿真等电路设计工作。 VHDL语言是由抽象及具体硬件级别进行描述的工业标准语言,它已经成为了一种通用硬件设计的交换媒介, 很多工程软件供应商已经把VHDL语言用做了EDA或CAD软件的输入/输出标准, 很多EDA厂商还提供了VHDL语言编译器, 同时在仿真工具、 布图工具及统合工具中对VHDL语言提供了支持。

VHDL语言具有描述能力强、模拟库函数和仿真语句丰富、 良好的层次化设计支持以及良好的可读性等优点; 当然, VHDL语言也存在着不足之处, 比如没有WAIT语句、不能处理动态结构、 不能等待时序等, 但它整体上的诸多优点为硬件设计带来了很大地方便,被很多用户所接受,也得到了诸多厂商的有力支持。

本章将通过全加器、 分频器、 键盘输入电路和数字钟等四个项目对VHDL语言在实际设计中的应用情况进行深入学习。

任务8.1 基本应用

8.1.1一位全加器的设计

加法器是数字系统中的基本逻辑器件,也是最基本的数字算法,无论是乘法、减法、除法或FFT运算最终也都要分解为加法运算。因此,加法器的设计是基础的设计之一。

首先了解一些关于加法器的基本知识:

(1)半加器的定义、真值表、逻辑表达式和元件符号。

(2)全加器的定义、真值表、逻辑表达式和元件符号。

(3)半加器与全加器的结构关系。

通过对加法器相关知识的分析和理解,找到一位全加器的设计方法。

从设计方案来看,一位全加器至少有4种设计方案,分别是:

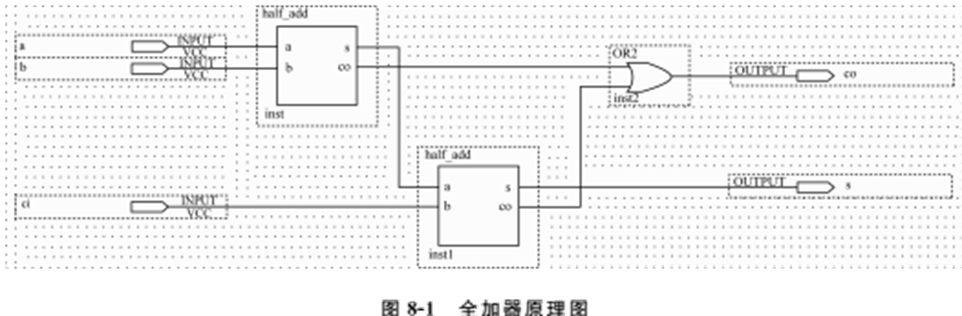

方案1:两个半加器级联获得一个一位全加器,如图8-1所示。

方案2:用VHDL语言的方法,直接描述其逻辑表达式,从而获得一位全加器。

方案3:用VHDL语言的方法,对一位全加器的真值表进行描述,从而获得一位全加器。

方案4:直接运用程序包ieee.std_logic_signed中定义的标准逻辑矢量的加法来实现一位全加器。

【提示】设计方案的优劣,可以通过编译报告中的输入/输出端口间的延时时间来进行比较。

方案4的具体设计步骤如下:

1.建立工程项目

打开QartusII软件,选择File->NewProject Wizard…弹出对话框,如图8-2所示。

继续单击Next按钮,并在对话框中输入项目路径、工程名和实体名,如图8-3所示。

继续单击Next按钮,出现对话框,如图8-4所示。

此步骤在本项目中不需要应用,直接单击Next按钮,进入下一步,进行器件选择,如图8-5所示。

选择Cyclone系列的器件EP1C3T144C8,点击Next继续,如图8-6所示。

工具设置使用默认选项,点击Next进入下一步,如图8-7所示。

工程项目建立完成,点击Finish结束。

2.建立VHDL文件

完成工程文件的建立之后,点击File->New…进入设计文件建立过程,选择VHDLFile,如图8-8所示。

点击OK按钮,完成VHDL文件建立。

点击File->save按钮,保存VHDL文件名,使其与工程名相同,进入VHDL文件编辑状态,如图8-9所示。

建立VHDL文件完成,进入VHDL文件的编辑。

3.编辑VHDL文件

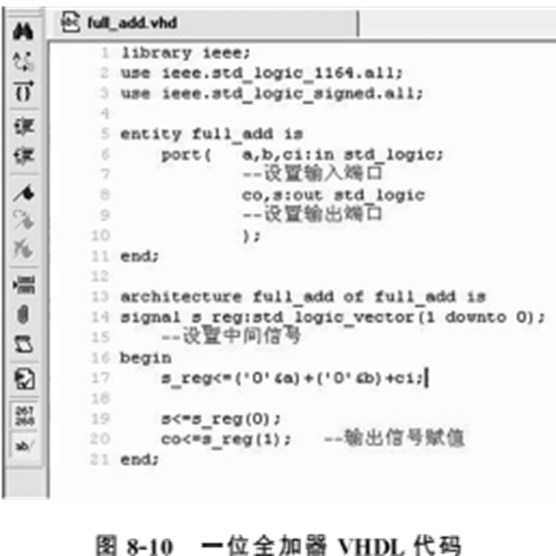

在VHDL编辑器下输入源代码,如图8-10所示。

libraryieee;

useieeestd_logic_1164all;

useieeestd_logic_signedall;

entityfull_addis

port(a,b,ci∶instd_logic;——设置输入端口

co,s∶outstd_logic——设置输出端口

);

end;

architecturefull_addof full_addis

signals_reg∶std_logic_vector(1downto0);——设置中间信号

begin

s_reg<=(‘0’&a)+(‘0’&b)+ci;

s<=s_reg(0);

co<=s_reg(1);——输出信号赋值

end;

4.编译

VHDL文件编辑完成后,点击Processing->StartCompilation或工具栏中的按钮进行编译,编译成功后如图8-11所示。

5.仿真

点击File->New…进入波形文件建立过程,根据图8-12的步骤建立波形仿真文件。

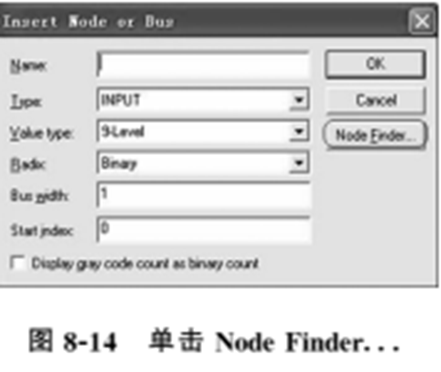

在图8-13指示的位置双击左键,向波形文件中导入输入输出端口,如图8-14所示,点击NodeFinder…,进入图8-15所示界面,并按①—④指示的步骤进行操作后,点击图8-16所示的OK按钮,完成输入输出端口导入。

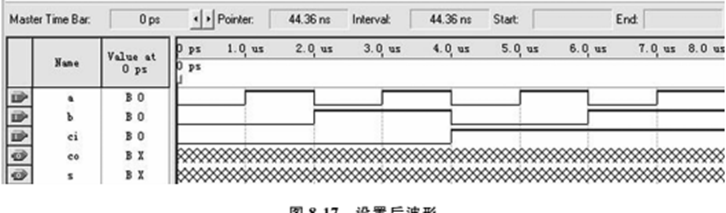

点击Eidt->EndTime…,设置仿真总时长为8us;点击Eidt->GridSize…设置单位时长1us;设置输入信号波形,如图8-17所示。

点击Processing->StartSimulation或按钮,开始仿真。

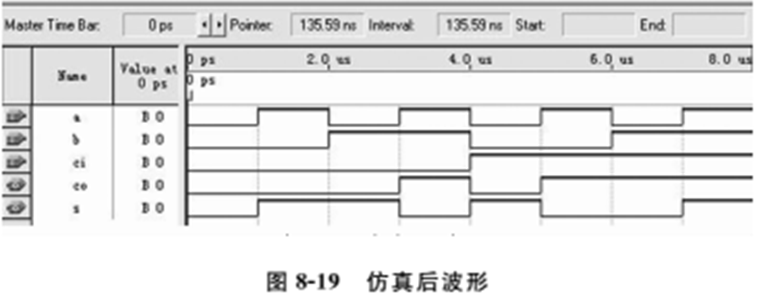

仿真完成后如图8-18,查看图8-19所示的仿真结果,核对设计的功能是否正确。