项目7 常用电路的硬件描述语言设计

数字电路可分为组合逻辑电路和时序逻辑电路。组合逻辑电路任一时刻的输出只决定于该时刻电路的输入组合, 而时序逻辑电路等逻辑门组合的输出不仅取决于当前输入, 还与过去的输入组合有关。组合逻辑电路可由与门或门和非门实现, 时序逻辑电路可由组合电路和触发器实现。 常用的组合逻辑电路有选择器、 编码器和译码器,常用的时序逻辑电路有触发器和计数器等。应用组合逻辑电路和时序逻辑电路, 可实现复杂的信号处理工作。 中央处理器的结构包含了加法器、 计数器、 译码器、选择器和寄存器等, 而寄存器就包含了触发器。

因此,掌握基本逻辑电路的设计, 将为复杂电路系统的设计打好基础, 而应用可编程逻辑器件和硬件描述语言可非常方便地实现基本逻辑电路功能。本章介绍常用逻辑电路的硬件描述语言设计。

任务7.1 常用组合逻辑电路的设计

7.1.1选择器的设计

【提示】首先根据电路的输入和输出情况定义端口,包括端口的名称、工作模式和数据类型,根据电路端口情况设计电路的实体。然后根据电路的功能设计电路的结构体,结构体的设计可采用RTL(寄存器传输逻辑)描述、行为描述和数据流描述三种方法。

三态是端口有高电平、低电平和高阻三种状态,在VHDL语言中,端口的高阻输出状态用‘Z’表示,端口的数据类型必须是标准逻辑类型(STD_LOGIC)。

使用双向端口时,若端口作为输入使用,必须将端口的输出状态设置为高阻态,否则从端口读取的数据会出错。

1.2 选1多路选择器的设计

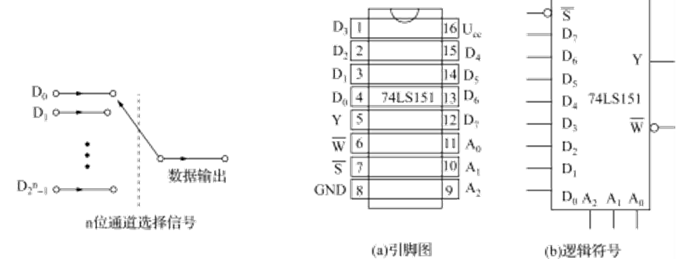

多路选择器能够根据需要将其中任意一路输入信号选出来,送到输出端。常用的IC包括8选1数据选择器(型号为74151、74LS151、74251、74LS151)。

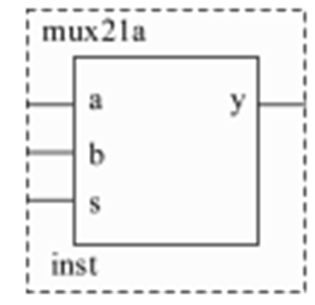

任务1:设计一个2选1多路选择器,电路框图如图7-3所示。

根据电路框图,对输入端口和输出端口进行定义:

因此2选1多路选择器实体可描述为:

ENTITY mux21a IS

PORT(a: IN BIT;

b:IN BIT;

s:IN BIT;

y:OUT BIT);

END mux21a;

结构体的设计可采用RTL(寄存器传输逻辑)描述、行为描述和数据流描述三种方法实现。

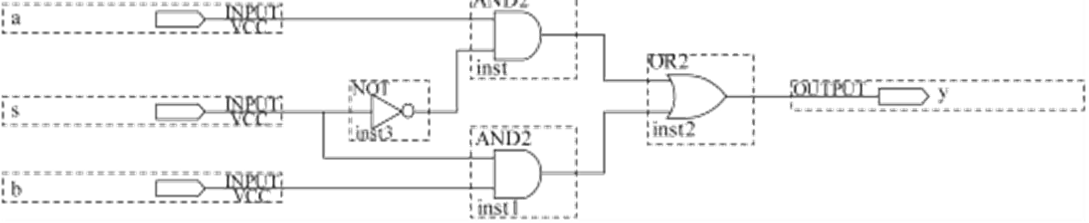

RTL描述:2选1多路选择器结构如图7-4所示,根据电路图,结构体可描述为:

ARCHITECTURE behav1 OF mux21a IS

BEGIN

y=(a AND NOT s) OR (b AND s);

END behav1;

【例7-1】

ENTITYmux21a IS

PORT(a:IN BIT;

b: IN BIT;

s: IN BIT;

y: OUT BIT);

ENDmux21a;

ARCHITECTUREbehav1 OF mux21a IS

BEGIN

y=(aAND NOT s) OR (b AND s);

ENDbehav1;

行为描述:直接描述2选1多路选择器的工作过程。利用并行条件语句,结构体可描述为:

ARCHITECTUREbehav2 OF mux21a IS

BEGIN

y<=aWHEN s=0 ELSE

b;

ENDbehav2;

【例7-2】

ENTITYmux21a S

PORT(a:IN BIT;

b: IN BIT;

s: IN BIT;

y: OUT BIT);

ENDmux21a;

ARCHITECTUREbehav2 OF mux21a IS

BEGIN

y<=aWHEN s=0 ELSE

b;

ENDbehav2;

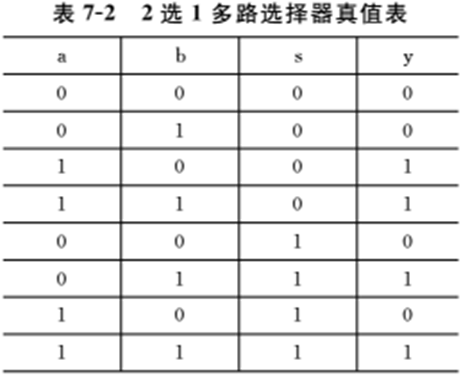

数据流描述:2选1多路选择器真值表如表7-2所示。

则结构体可描述为:

ARCHITECTUREbehav3 OF mux21a IS

SINGALt: BIT_VECTOR(2 DOWNTO 0);

BEGIN

t<=a& b & s;

WITHt SELECT

y<=‘0’WHEN “000”,

‘0’WHEN “001”,

‘0’WHEN “010”,

‘1’WHEN “011”,

‘1’WHEN “100”,

‘0’WHEN “101”,

‘1’WHEN “110”,

‘1’WHEN A“111”;

ENDbehav3;

【例7-3】

ENTITYmux21a IS

PORT(a:IN BIT;

b: IN BIT;

s: IN BIT;

y: OUT BIT);

ENDmux21a;

ARCHITECTUREbehav3 OF mux21a IS

SINGALt: BIT_VECTOR(2 DOWNTO 0);

BEGIN

t<=a& b & s;

WITHt SELECT

y<=‘0’WHEN “000”,

‘0’ WHEN “001”,

‘0’ WHEN “010”,

‘1’ WHEN “011”,

‘1’ WHEN “100”,

‘0’ WHEN “101”,

‘1’ WHEN “110”,

‘1’ WHEN “111”; END behav3;

7.1.2 双向三态电路的设计

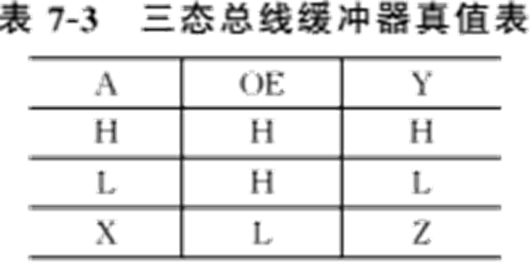

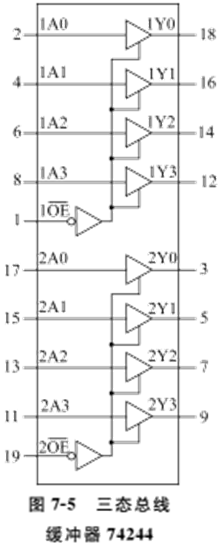

所谓三态,即输出端状态除了高低电平外,还可以是高阻状态;74244是典型的三态总线缓冲器,如图7-5所示。三态缓冲器真值表如表7-3所示。

在VHDL语言中,高阻状态用值‘Z‘表示,此时输出信号必须定义为标准逻辑类型。

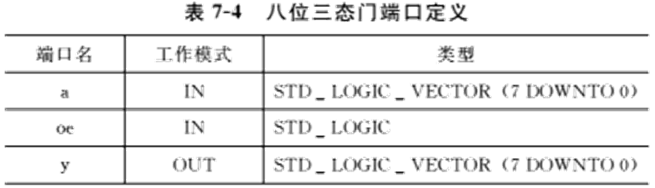

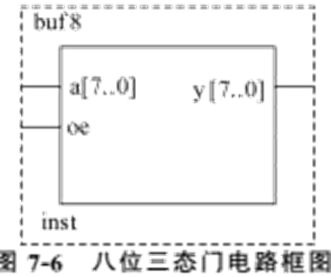

任务2:设计八位三态门,电路框图如图7-6所示。根据电路框图,对输入端口和输出端口进行定义:

因此实体可表示为:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYbuf8 IS

PORT(a: IN STD_LOGIC_VECTOR(7 DOWNTO 0);

oe:IN STD_LOGIC;

y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

ENDbuf8;

根据三态门的功能,结构体可表示为:

ARCHITECTUREbehavOF buf8 IS

BEGIN

PROCESS(a,oe)

BEGIN

IFoe=‘0’THEN

y<=(OTHERS=>‘Z’);

ELSE

y<=a;

ENDIF;END PROCESS;END behav;

【例7-4】

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYbuf8 IS

PORT(a: IN STD_LOGIC_VECTOR(7 DOWNTO 0);

oe:IN STD_LOGIC;

y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

ENDbuf8;

ARCHITECTUREbehavOF buf8 IS

BEGIN

PROCESS(a,oe)

BEGIN

IFoe=‘0’THEN

y<=(OTHERS=>‘Z’);

ELSE

y<=a;

ENDIF;

ENDPROCESS;

ENDbehav;

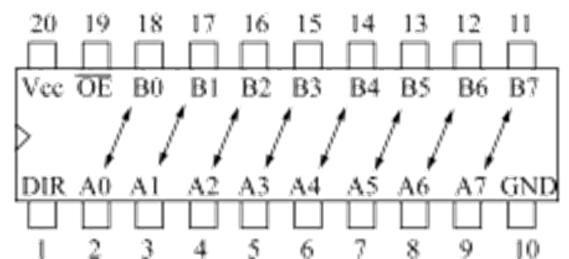

所谓双向电路,典型芯片如74245,当DIR为低电平时,信号从A流向B;当DIR为高电平时,信号从B流向A,如图7-7所示。

因此双向电路结构体改为:

ARCHITECTUREbehav2 OF dr4 IS

BEGIN

PROCESS(a,b,dir)

BEGIN

IFdir=‘0’THEN

b<=a;

a<=“ZZZZ”;

ELSE

a<=b;

b<=“ZZZZ”;

ENDIF;

ENDPROCESS;

ENDbehav2;

双向电路完整程序为例7-8所示,电路结构如图7-12所示,由图7-12可见,电路为双向电路。