任务5.3 嵌入式逻辑分析仪SignalTap II的使用

为了使得设计尽快投入市场,设计人员需要一种简易有效的测试工具,以尽可能地缩短测试时间。传统的逻辑分析仪在测试复杂的FPGA设计时,将会面临以下几点问题:(1)缺少空余I/O引脚。设计中器件的选择依据设计规模而定,通常所选器件的I/O引脚数目和设计的需求是恰好匹配的。(2)I/O引脚难以引出。设计者为减小电路板的面积,大都采用细间距工艺技术,在不改变PCB板布线的情况下引出I/O引脚非常困难。(3)外接逻辑分析仪有改变FPGA设计中信号原来状态的可能,因此难以保证信号的正确性。(4)传统的逻辑分析仪价格昂贵,将会加重设计方的经济负担。

5.3.1基本使用方法

下面以开关电路为例介绍SignalTapII的基本使用流程。

以下是开关电路的VHDL程序

libraryieee;

useieeestd_logic_1164all;

entityswitchsis

Port(sw∶instd_logic_vector(7downto0);

clk∶instd_logic;

led∶outstd_logic_vector(7downto0));

endswitchs;

architecturebehave of switchsis

signalle∶std_logic_vector(7downto0);

begin

process(clk)

begin

if(clkeventand clk=“1”)thenle<=sw;endif;

endprocess;

led<=le;

endbehave;

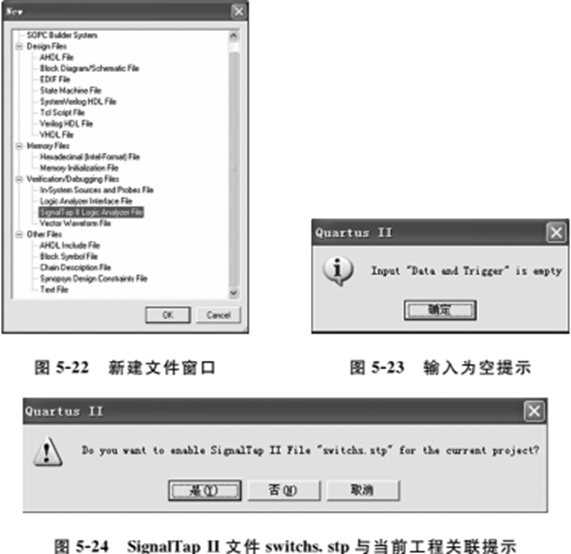

1.建立SignalTap II (.stp)文件并加入工程。

【提示】如果我们需要在工程中使用该SignalTapII文件,或者不使用SignalTapII逻辑分析仪,在QuartusII界面中选择Assignments>Settings。然后在打开窗口左边的分类列表中选择SignalTapII Logic Analyzer。可以把EnableSignalTapII Logic Analyzer前面的勾去掉来关闭逻辑分析仪。在一个工程中可能同时会有多个SignalTap文件,但在同一时刻只能有一个有效。多个SignalTapII文件是非常有用的,比如工程很大,在工程中不同的部分都需要用SignalTapII来捕捉信号,这样探测不同的部分时我们只需要使用不同的SignalTapII文件就可以了,避免反复设定SignalTapII文件。按照步骤1可以建立新的SignalTapII文件,不同的SignalTapII文件拥有不同的文件名。

如果要改变当前工程中已经关联的SignalTapII文件,在SignalTapII Logic Analyzer窗口中的SignalTapII File name

选择框中点右边的浏览按钮,选择所需要的SignalTapII文件,然后点击Open,最后点击OK就可以了。

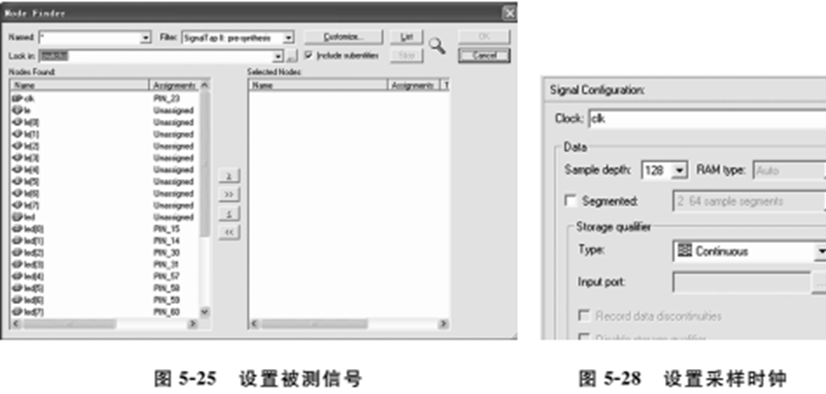

2.设置被测信号。

3.设置采样时钟。

4.设置触发条件。

5.建立硬件环境。

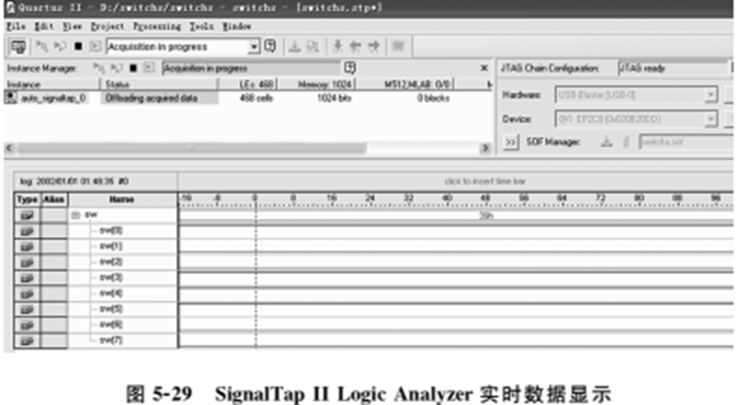

6.在SignalTapII窗口,浏览找到下载文件将其下载至开发板,之后选择Processing>RunAnalysis或者单击图标。接着,单击SignalTapII窗口中的Data标签页。这时SignalTapII Instance Manager面板中状态Status中显示“Waitingfor trigger”,这是因为触发条件没有满足。

5.3.2多级触发使用

在这部分中,设置SignalTapII的触发条件为:当开关0、1、2、3的值依次从0变为1,即开关0-3的上升沿按顺序到来时。

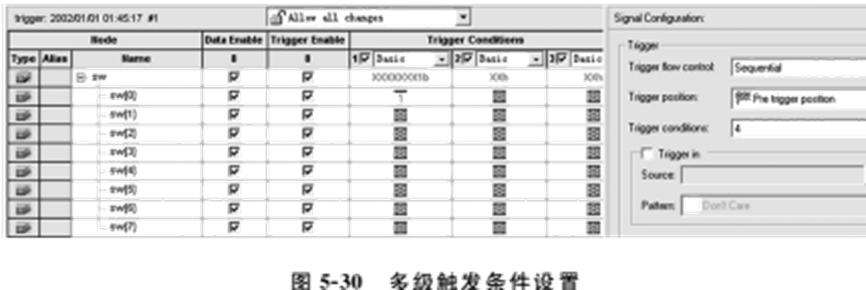

1.在SignalConfiguration面板中,在TriggerConditions下拉菜单中选择4,如图5-30所示

2.右键点击触发条件1中对应SW[0]的单元,并选择上升沿RisingEdge。进行同样的操作把触发条件2中SW[1],触发条件3中SW[2]和触发条件4中SW[3]的触发条件设为RisingEdge。这时,我们得到如图5-31所示的Setup标签页界面。

3.重新编译整个工程然后把配置文件重新下载到开发板上。

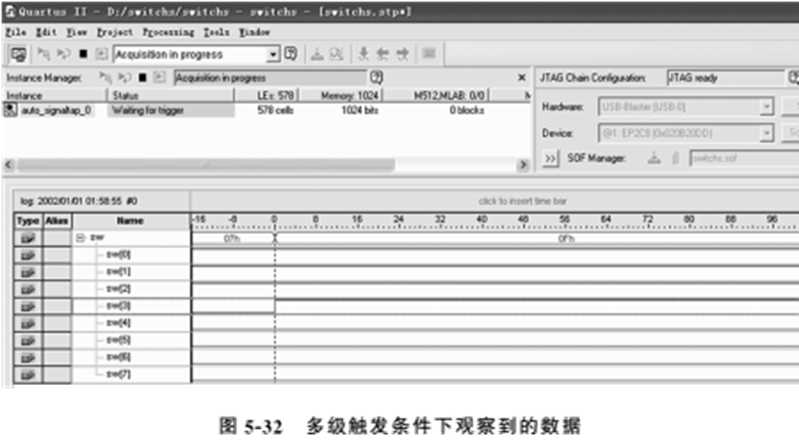

4.回到SignalTapII窗口,单击Data标签页,然后点击Processing>RunAnalysis。注意到窗口显示状态将一直会是“Waitingfor trigger”,直到满足相应的触发条件。接下来,依次把开关的值从0设为1,开关1的值从0设为1,开关2的值从0设为1,开关3的值从0设为1。完成这些工作后,我们将会观察到如图5-32所示的所有开关的值。我们可以按照上述方法建立不同的触发条件,然后在开发板上检验这些触发条件。

5.3.3高级触发使用

这次,我们将把触发条件设为:当开关0、开关1和开关2中的任何一个发生跳变(上升沿或下降沿)。这意味着当这3个开关中其中一个的值改变时,逻辑分析仪将会更新显示所有观察信号的值。注意,我们可以把要观察信号的不同组合逻辑功能作为逻辑分析仪的触发条件。

1.单击Setup标签页,在SignalConfiguration面板中确认TriggerConditions值为1。

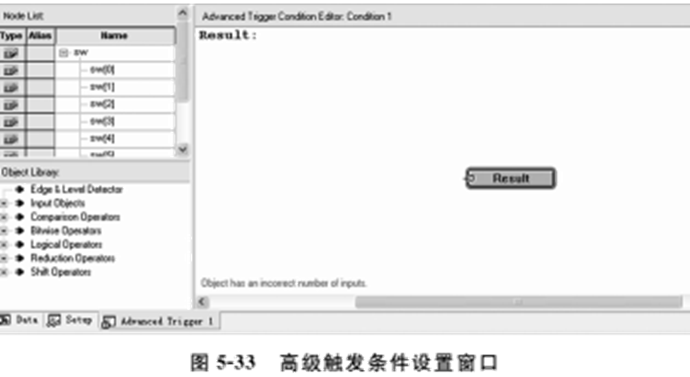

2.在信号节点列表中的TriggerConditions列中,确认TriggerConditions复选框已经选中,然后在下拉菜单中选择Advanced。这时弹出如图5-33所示的窗口,该窗口允许使用SignalTapII中观察的信号节点中的不同信号来建立一个逻辑电路,作为触发条件。

3.在图5-33窗口的NodeList部分中,选中SW[0],SW[1]和SW[2],然后把它们拖曳到右边空白处的AdvancedTrigger窗口。注意,我们也可以单独地对每个信号节点进行拖入。

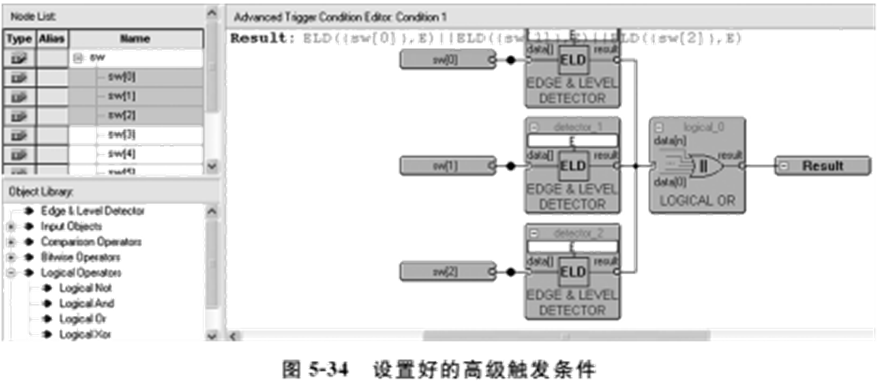

4.我们需要添加必需的逻辑运算符到电路中。根据触发条件我们需要1个OR门和3个边沿检测器。单击左下ObjectLibrary窗口LogicalOperators左边的+号,可以找到OR门,然后把OR门拖入到AdvancedTrigger Condition Editor窗口中。单击Edge& Level Edtector并把它拖入编辑窗口中。重复3次,然后把这些元件组成如图5-34所示的电路。3个输入SW[0]、SW[1]和SW[2]分别和3个edgeand level detector连接,3个detector的输出再和OR门相连,OR门的输出连接到输出脚Result上,输出脚本身就已经在编辑窗口中了。

5.我们现在需要设置每个edgeand level detector,让它们都能检测到下降沿或者上升沿。双击第一个detector,在Setting输入框中输入E然后单击OK。这代表着当输入出现下降沿或者上升沿时,detector的输出为1。重复上诉步骤设置第二和第三个detector。

6.重新编译工程然后下载至开发板。接下来按照之前的方法运行SignalTapII。我们应该会注意到,每当板上的开关0、1、2中其中一个的值发生改变,SignalTapII逻辑分析仪都将会被触发。

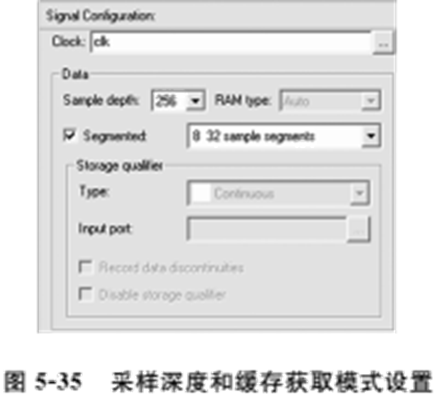

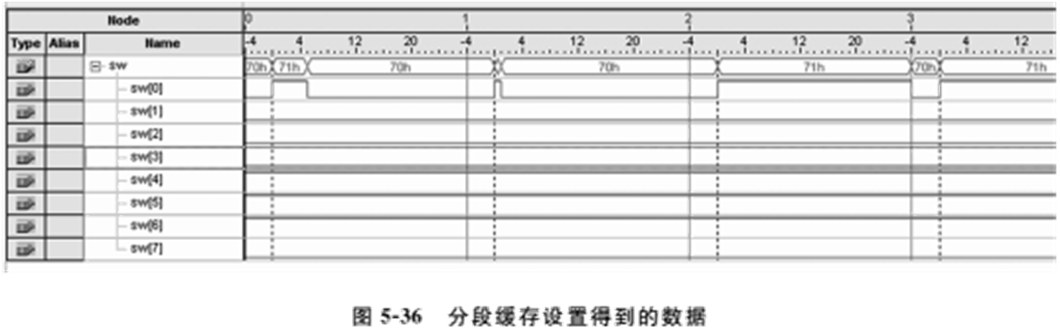

5.3.4采样深度和缓存获取模式

分段缓存允许我们把数据获取缓存分成几个独立并划分好大小的部分。本例中,我们将把采样深度为256bits的缓存分成8个32bits的部分。这样将会允许我们捕捉发生在8个连续触发时间附近的8个不同事件。

1.把触发配置设回Basic并只有一级触发,触发条件为SW[0]的跳变沿。

2.在SignalTapII窗口中的SignalConfiguration面板中的Data面板的SampleDepth下拉菜单中选择256。这个选项允许我们指定在我们的设计中的触发时刻附近总共有多少个采样点。如果我们需要更多的采样点来调试我们的设计,可以选择更大的采样深度。注意:如果采样深度选择过大,在我们的设计中将可能会不够资源来实现,这样,设计就会编译不过。如果这种情况发生,请减小采样深度的大小。

3.在SignalTapII窗口的SignalConfiguration面板中的Data部分,选中Segmented。然后在Segmented右边的下拉菜单中,选择832 sample segments。完成后的界面如图5-35所示。

4.重新编译工程并加载下载文件。好了,我们可以使用分段获取模式SegmentedAcquistionmode来观察我们的设计。

5.回到SignalTapII窗口并单击Processing>RunAnalysis。现在,反复拨动开关SW[0]并在两次拨动之间改变其他7个开关的值。当我们完成8次SW[0]的值改变时,采样缓存中的值将显示在data窗口中,这些显示的采样值是8个开关在触发时刻附近的数值。波形如图5-36所示。