任务3.4 数据域仪器的使用

3.4.1 信号发生器的使用

1.函数信号发生器

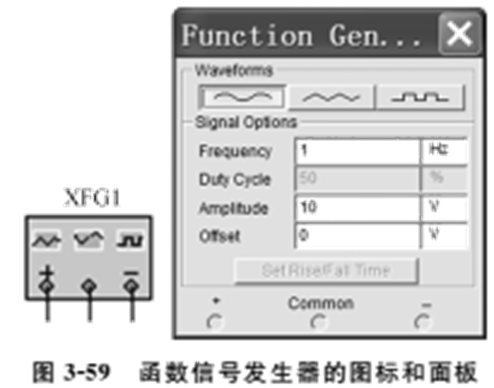

(1)函数信号发生器的图标及面板。

如图所示为函数信号发生器的图标和面板,它主要用来产生正弦波、方波和三角波信号。

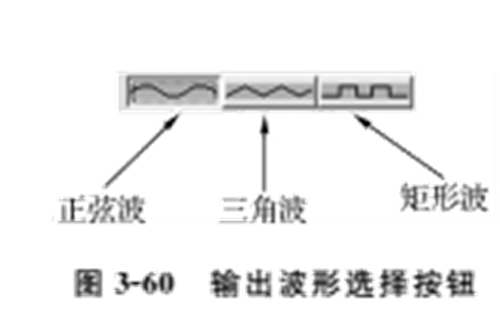

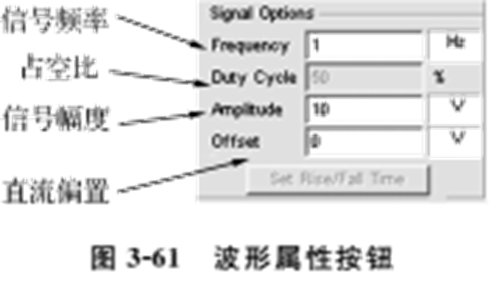

函数信号发生器面板上部的三个波形选择按钮,用于选择仪器产生波形的类型。中间的几个选项窗口,设置波形属性。

函数信号发生器面板下部的三个接线端子,通常COM端连接电路的参考地点,“+”为正波形端,“—”为负波形端,可同时输出两个相位相反的信号(相对COM端)。

Amplitude信号峰值设置:与信号直流偏置有关。设置范围:1μV~ 999kV。

DutyCycle占空比设置:该参数设置只对三角波和方波有效,对正弦波信号无效(变为灰色)。可调范围为1%~ 99%。

Offset偏置电压值设置:即把正弦波、三角波、方波叠加在设置的偏置电压上输出,其可选范围为:-999kV与999kV。

SetRise/Fall Time按钮:设置方波信号的上升时间与下降时间。

(2)面板操作。

在进行电路模拟仿真的同时可以同步进行调节信号发生器的有关参数,直接观察输出数据波形的变化现象,这些信号的频率调节范围很宽,可从音频调到射频。函数信号发生器的输出信号参数范围如表3-1所示。

(3)连接。

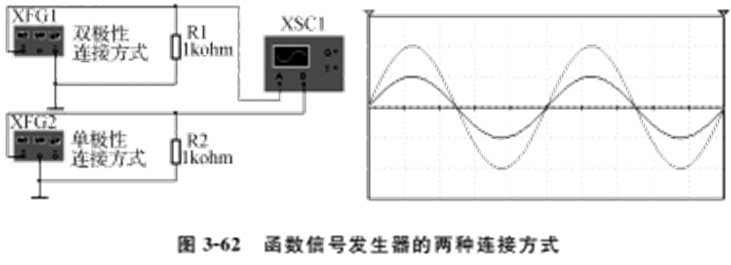

单极性连接方式(一般用于普通电路):

①连接+和Common端子,输出信号为正极性信号,峰—峰值等于2倍幅值。

②连接Common和-端子,输出信号为负极性信号,峰—峰值等于2倍幅值。

双极性连接方式(一般用于信号发生器与差分电路相连,如差动放大器、运算放大器等)。

③连接+和-端子,输出信号峰—峰值等于4倍幅值。

④同时连接+、Common和-端子,且把Common端子与公共地符号相连,则输出两个幅度相等、极性相反的信号。

图3-61所示为函数信号发生器的两种连接方式,两个信号发生器的参数设置相同,均为输出频率1kHz,幅度2V的正弦波,它们分别接到示波器的A、B通道,示波器的两通道参数设置也相同,从输出波形看,双极性连接方式输出信号的幅度为单极性连接方式输出信号幅度的2倍。

2.字信号发生器

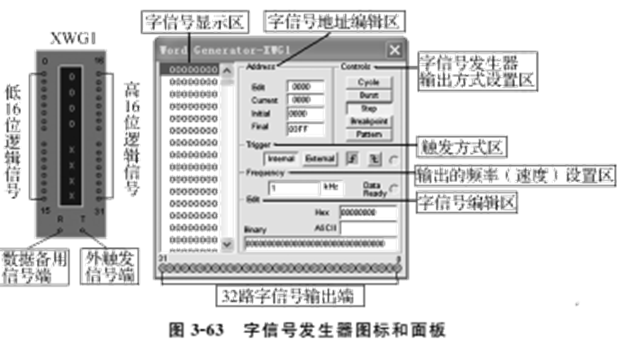

字信号发生器(WordGenerator)是一种能够产生32路同步逻辑信号的仪器。可以用来对数字逻辑电路进行测试,实际上是一个数字激励源编辑器,其图标和面板图如图3-63所示。

字信号发生器的图标有32个输出端,其中的每一个端子都可接入数字电路的输入端。

R端子:数据备用信号端(Ready)。

T端子:外触发信号端。

(1)字信号发生器使用设置如下:

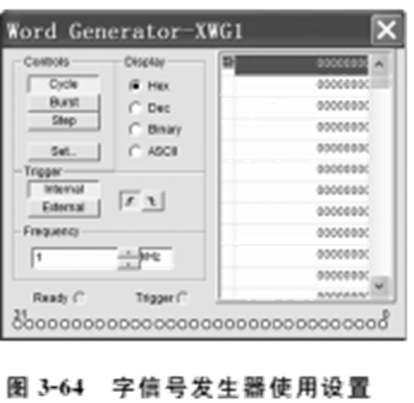

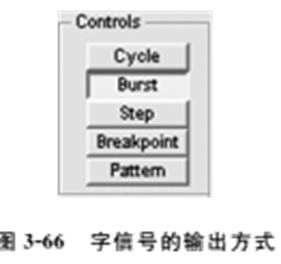

①trols区:

Cycle:循环输出。

Burst:猝发输出。

Setp(单步):表示每单击鼠标左键一次输出一条字信号。

②Display区:

Hex十六进制

Dec十进制

Binary二进制

ASCIIASCII码

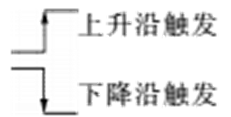

③Trigger区触发方式:

Intemal内触发

Extemal外触发

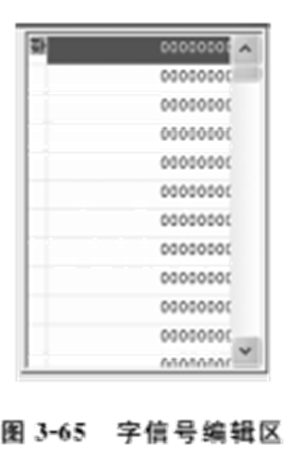

④字信号编辑区:

面板的最右侧是字信号编辑区,对32位的字信号进行编辑和存放。编辑区地址范围为0000H-03FFH,共计1024条字信号。利用鼠标器移动滚动条可使编辑区内的显示内容上下移动。鼠标左键单击某一条字信号即可实现对其定位和写入或修改。

3.字信号输出方式设置

字信号的输出方式分为3种:

Step表示单步输出。

Burst表示字信号是从首地址开始至末地址连续逐条单循环的输出字信号。

Cycle表示循环不断进行Burst方式的字信号输出。

在Burst和Cycle状态下可设置中断点,通过光标选中某一地址的字信号后,单击Breakpoint实现,设置为中断点的字信号在显示区中以*号显示,当运行至该地址时输出暂停,单击Burst或Cycle则恢复输出。

◆Clearbuffer复选框:用于设置是否清除字信号编辑区的内容。

◆Open复选框:用于打开存有字信号内容的字信号文件,其扩展名为.dp。

◆Save复选框:用于保存字信号的内容,其文件的扩展名为.dp。

◆Up Counter复选框:设置输出递增编码的字信号。

◆Down Counter复选框:设置输出递减编码的字信号。

◆Shift Right复选框:设置输出右移编码字信号。

◆Shift Left复选框:设置输出左移编码字信号。

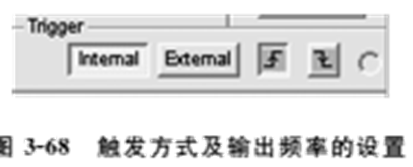

4.触发方式及输出频率的设置

字信号发生器有两种触发方式:Internal(内部)和External(外部)。

Frequency区用于设置字信号输出频率,在Burst和Cycle状态下的输出快慢由设定的输出频率决定。为了保持同步,往往用DataReady端(数据准备就绪)指示。

5.字信号的编辑

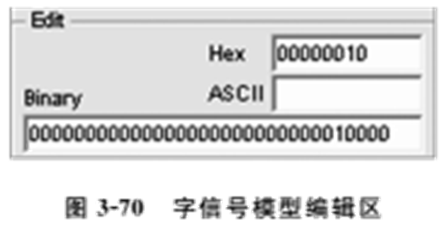

当进行字信号编辑时,在显示区中用鼠标选择编辑位置,当前编辑的地址可以在Address区的Edit栏中看出,然后在字信号模型编辑区的Hex栏中以16进制数输入数据,或者ASCII栏以ASCII码输入数据,或者在Binary栏以二进制数输入数据,显示区中相应位置显示已设定的字信号模型。

3.4.2 逻辑分析仪的使用

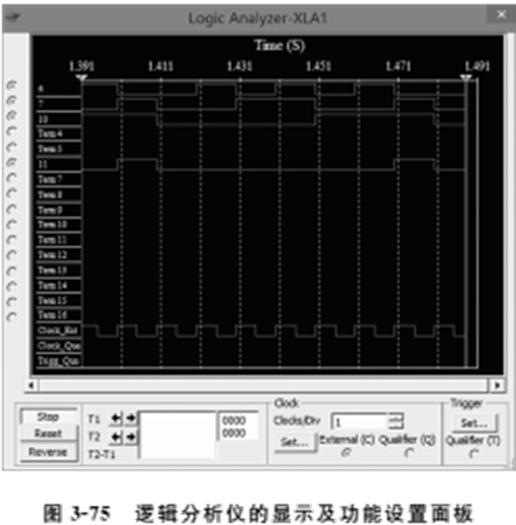

Multisim的逻辑分析仪(LogicAnalyzer)可以对数字逻辑信号的高速采集和时序分析。逻辑分析仪(LogicAnalyzer)可以同步显示和记录16路逻辑信号,如图3-74所示,逻辑分析仪的图标左侧有1~F共16个输入端,使用时接到被测电路的相关节点。图标下部也有3个端子,C是外时钟输入端,Q是时钟控制输入端,T是触发控制输入端。

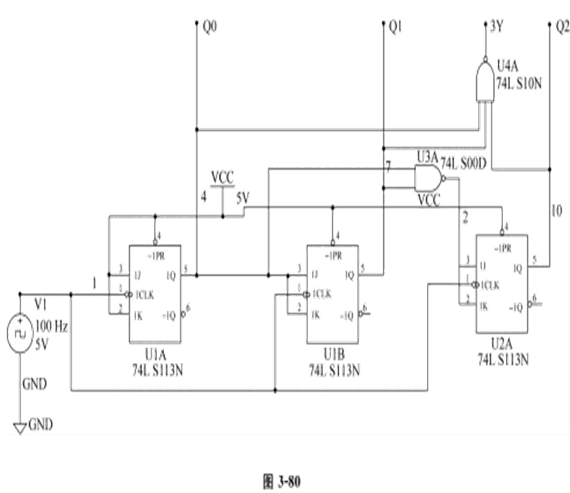

下面以JK触发器设计的同步七进制计数器为例说明逻辑分析仪(LogicAnalyzer)的功能及使用方法。

设计过程分析:

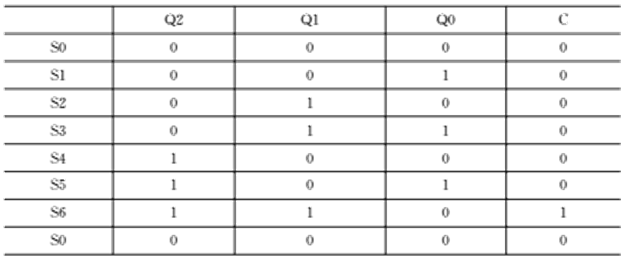

设七进制计数器的状态为S0~S6,M=7,取进位信号为输出逻辑变量,当产生进位时C=1,无进位时C=0。

(1)确定触发器的个数,由于M=7,故取3个JK触发器,因为22<7<23。

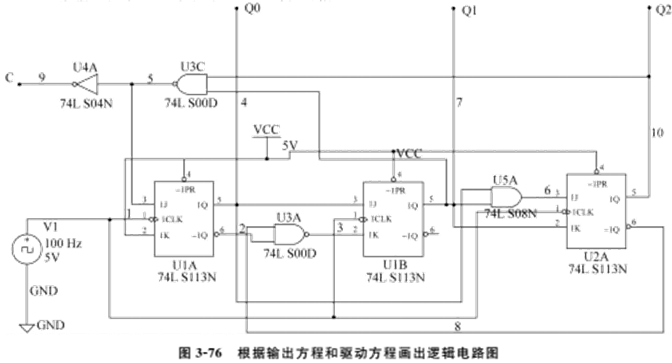

(2)设触发器的状态分别为Q2,Q1,Q0,根据设计要求列出状态表。

由电路的状态表画出的电路时序表如图3-75所示。

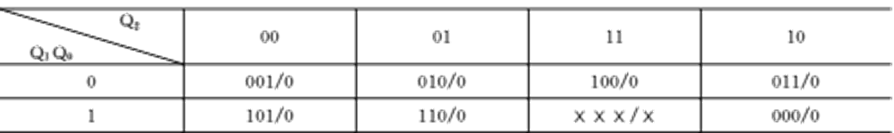

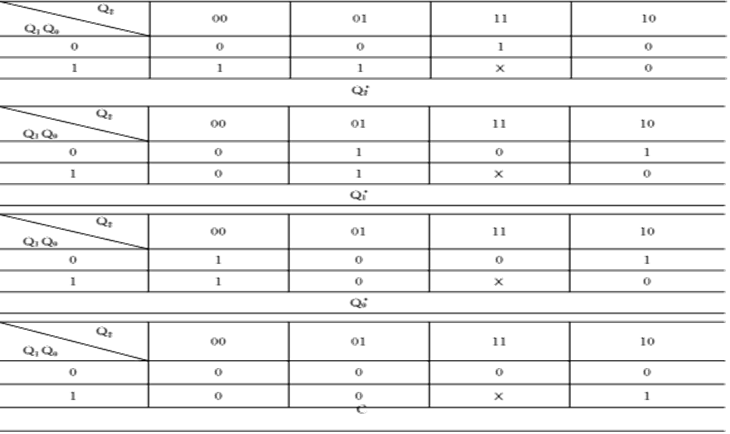

(3)根据状态表画出卡诺图,由于在计数器工作过程中不会出现(111)这个状态,故可将Q2Q1Q0这个最小项作为无关项处理。

将此卡诺图分解可分别得到触发器次态Q*2,Q*1,Q*0,和进位输出C与触发器初态Q2Q2,Q1,Q1,Q0之间逻辑关系的卡诺图。

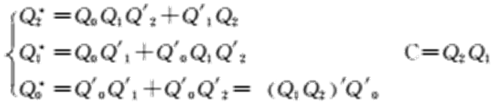

由以上各卡诺图化简后得到触发器的状态方程和输出方程。

(4)将以上触发器的状态方程与JK触发器的特性方程 作比较,即可得到触发器的驱动方程

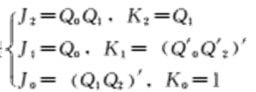

根据输出方程和驱动方程画出逻辑电路如图3-76所示。

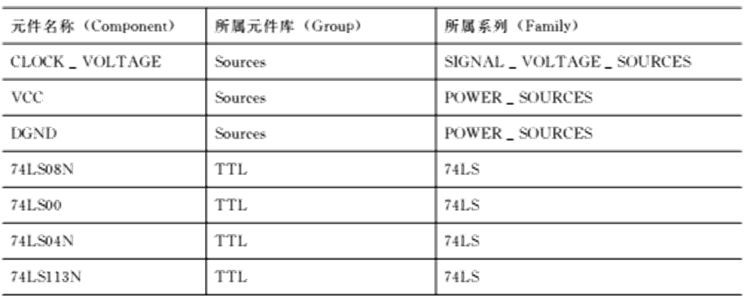

新建文件,根据图3-75画电路图,仿真元件信息如下表所列。

(5)放置逻辑分析仪(LogicAnalyzer)。

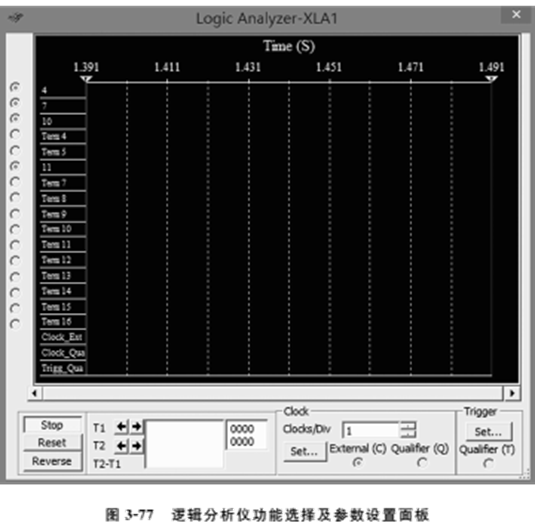

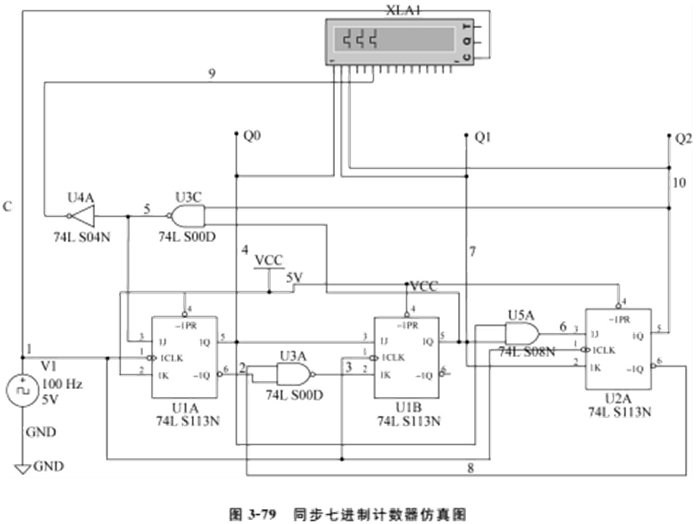

单击仪器仪表(Instruments)工具栏中的逻辑分析仪(LogicAnalyzer),将Q0,Q1,Q2连接到逻辑分析仪的输入端1,2,3,C连接到逻辑分析仪的输入端6,时钟信号V1频率设置为100Hz,逻辑分析仪的外时钟输入端C连接时钟信号V1。双击逻辑分析仪,将弹出如图3-77所示的逻辑分析仪功能选择及参数设置面板,单击时钟设置按钮(SetupClock),弹出时钟设置(ClockSetup)对话框。设置逻辑分析仪的信号源(ClockSource)为外部(External),如图3-78所示,单击确定(Accept)按钮。

编辑好的同步七进制计数器电路图如图3-79所示。系统仿真,观察逻辑分析仪的信号。

实训任务

试画出图3-80中电路输出端Y,Q2,Q1,Q0的波形分析该电路功能。