职称:教授

单位:江苏大学

部门:计算机学院

主讲教师:肖铁军 赵蕙

教师团队:共2位

| 学校: | 江苏大学 |

| 开课院系: | 计算机科学与通信工程学院 |

| 学分: | 2 |

| 课时: | 64 |

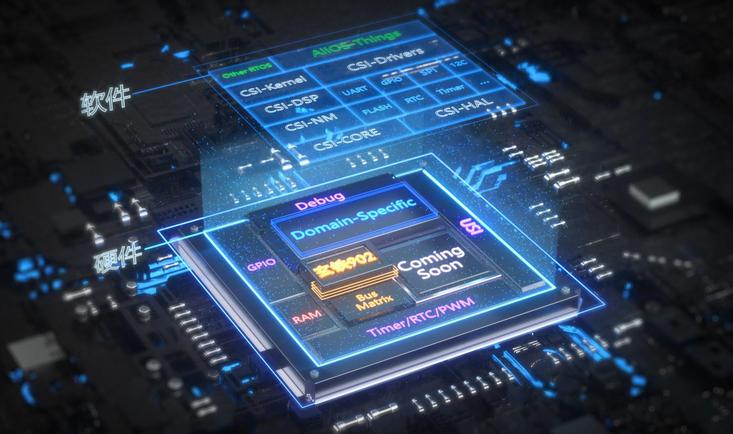

信息技术在当今社会发挥着越来越重要的作用,而CPU作为其中核心技术之一,它的结构原理是计算机领域从业人员必备的专业知识。本实验课程吸收了计算机体系结构领域的新发展成果,以极具发展潜力的RISC-V作为CPU设计的目标,从基本的计算机部件开始,进一步设计CPU数据通路及控制器,并利用口袋实验板或远程FPGA实验平台进行验证调试。 通过学习和训练,可以基本掌握Verilog/SystemVerilog硬件描述语言,能够用硬件描述语言设计逻辑电路和计算机部件,从设计的角度深刻理解CPU硬件结构和指令系统之间的内在联系,了解CPU的组织结构和工作原理。同时通过实践提升动手能力和分析问题、解决问题的能力,培养创新意识。 本课程采用“范例-任务”教学法,每个实验都会先给出一个参考范例,再布置一个相关的设计任务,并配有视频讲解和演示;实验项目环环相扣、循序渐进,像堆积木一样逐渐完成CPU设计。可作为《计算机组成原理》等课程的实验项目;低起点、高落点、循序渐近的实验设计,使得该实验课程也适用于对CPU感兴趣的社会学习者。